# **CHAPTER 1**

# **INTRODUCTION**

This dissertation describes an environment for the evaluation of computer architectures and architectural features. The first chapter provides background information for the problem of obtaining program measurements. Initially, limitations of past architectural studies are described and the goals for the dissertation are stated. This is followed by a review of the area of obtaining program measurements. First, the different classes of program measurements are characterized. Next, the methods used in the past for obtaining program measurements are described and their strengths and weaknesses are identified. The applications of analyzing program measurements are then examined and past studies using program measurements and their contributions are discussed.

The second chapter describes the environment that was constructed for obtaining architecturallevel measurements. The modifications to an existing retargetable optimizer are illustrated and the manner in which reports are generated from the information collected is shown.

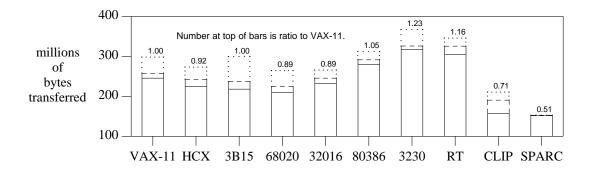

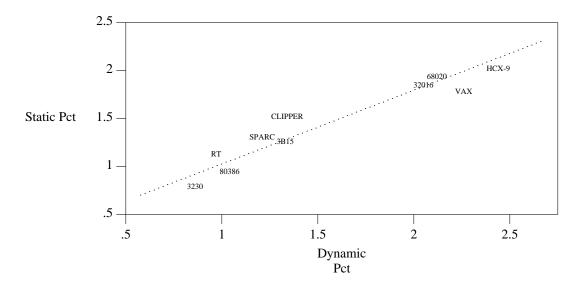

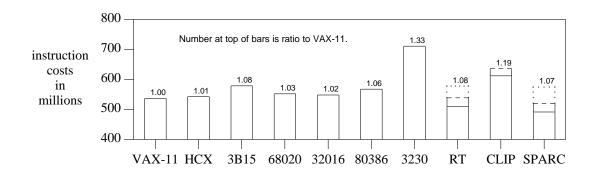

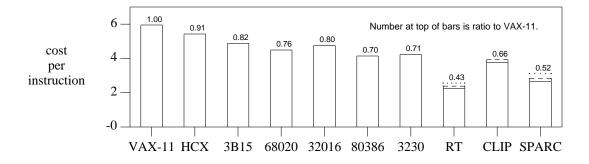

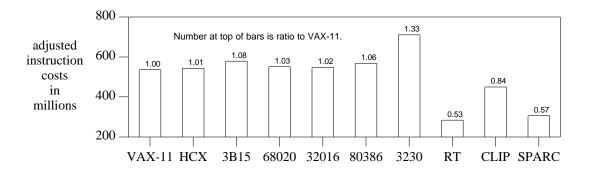

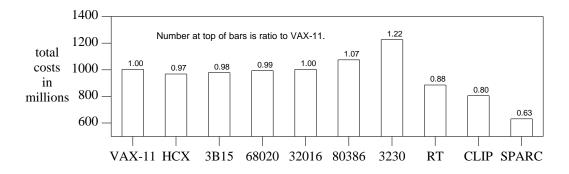

The third chapter describes an architectural study performed with this environment that analyzed measurements collected from the execution of the same set of test programs on each machine. First, the different kinds of measurements extracted from each architecture are discussed, background information about each of the architectures in the study is given, and the set of test programs used in the study is specified. The measurements obtained from the architectures are then analyzed. The dynamic measurements are first examined and the implications of this information are discussed. Static measurements are then compared to the corresponding dynamic measurements. Strong linear relationships between most of the static and dynamic measurement, which give more useful information on performance, from its corresponding static measurement, which are easier to obtain. The last section in this chapter compares each of the architectures by attempting to determine the total cost of the execution of the test set.

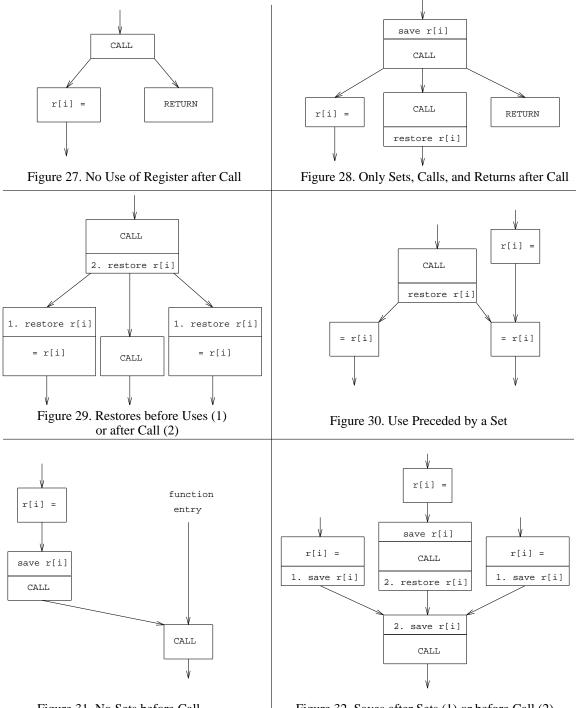

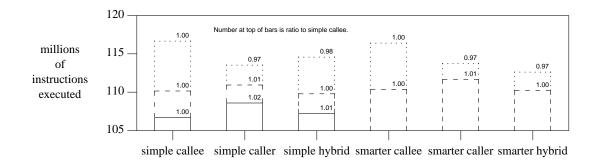

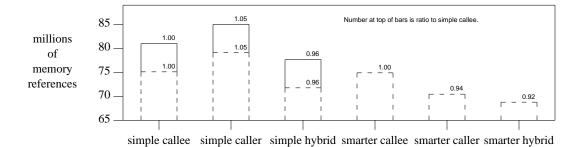

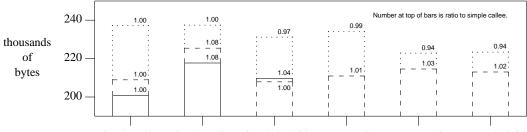

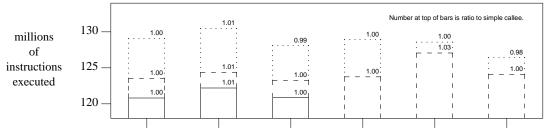

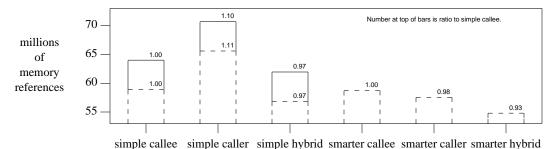

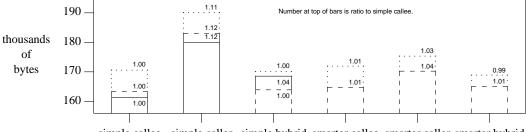

The fourth chapter describes some interesting experiments performed with the environment. The first experiment analyzed six different methods for saving and restoring registers. In one set three of the schemes do not use data flow analysis to minimize the number of saves and restores, while the three schemes in the other set do. Within each set a callee save, caller save, and hybrid approach are used. The next experiment evaluates the effectiveness of passing arguments in registers as a calling sequence convention. The following experiment abandons complex call and return instructions in favor of more primitive instructions. The combination of passing arguments through registers and using more primitive instructions allowed new optimizations to be accomplished on a significant percentage of the executed calls. The last experiment analyzed the effectiveness of a new technique for reducing the cost of branches by using registers. This technique has the advantages of reducing the number of instructions executed, eliminating many pipeline delays, and potentially decreasing the delay due to instruction cache misses.

The final chapter gives conclusions for the dissertation. The achievement of the goals of the dissertation and contributions of this research are discussed.

## 1.1. Motivation

To effectively evaluate an existing or proposed computer architecture, one must analyze measurements from typical programs that are to be executed by the machine. The analysis of these measurements can be used to determine the influence of a specific feature on the effectiveness of the architecture and to compare different architectures. The method used to extract these measurements can impact the accuracy and quality of architectural evaluations.

Past architectural studies have suffered from one or more limitations due to the methods used for collecting program measurements. Methods such as simulation and tracing are very time-consuming and the use of these methods can result in studies analyzing only a small number of executed instructions. Some studies have compared different architectures without consideration of the compiler for each machine. Since the quality of the code produced by different compilers can vary, these studies are comparing compilers along with architectures. The implementation of several methods for the extraction of

program measurements can require much effort and time. For instance, the effort to construct a simulator is comparable to the effort to construct a compiler. The difficulty of implementing these methods may discourage one from collecting program measurements for architectural evaluations. The extraction of specific measurements using some methods can be difficult or impossible. Lack of detailed information can lead to assumptions that may be inaccurate. Many methods prohibit experimentation with an architectural feature or an architecture that does not yet exist. Such experimentation is vital since it produces empirical results that can guide architectural design. Thus, some limitations of previous architectural studies include:

- 1. a small set of benchmark programs

- 2. differences in how machine instructions are produced

- 3. excessive effort required to implement a method to extract measurements

- 4. inability to obtain certain types of measurements

- 5. difficulty in performing experiments

The last major architectural study that evaluated several different architectures, the CFA evaluations [FuB77], was performed over thirteen years ago. The CFA evaluations collected a few detailed measurements from a set of small programs. Many current architectures are now quite different from the architectures in the previous decade. A thorough evaluation of several current architectures would provide valuable information to computer architects for modification of existing machines and design of new ones.

An environment that quickly collects accurate and detailed dynamic measurements from programs and facilitates experimentation can aid in the interactions between the design of an architecture and a compiler. An architecture is often designed first without determining if a compiler can make effective use of the features of the architecture. One area that typifies this problem is the calling sequence conventions imposed by the writer of the compiler and run-time library. These conventions often seem to be imposed as an afterthought with little analysis and are typically restricted by the available instructions on the machine for implementing function calls and returns. Using an environment that facilitates the joint development of an architecture and compiler can result in a more effective implementation. There are three goals for this research. The first goal is to provide an environment in which static and dynamic architectural-level program measurements can be collected without the problems of past architectural studies. These program measurements include the frequency of occurrence of instructions and addressing modes, program size information, and register usage. A more detailed description of the types of measurements is given in a later section. The second goal is to use this environment to perform an architectural study on several current architectures. This study analyzes the dynamic measurements collected from each of the architectures and examine the differences between static and dynamic measurements. The last goal is to use the environment to perform experiments in code generation and machine design. These experiments not only provide insight on the influence of some architectural features and conventions, but also demonstrate the effectiveness and utility of the environment and suggest areas in which the environment can be extended.

### 1.2. Review

Classes of program measurements, different methods of obtaining program measurements, applications of analyzing program measurements, and previous studies using program measurements are examined in the following sections.

#### 1.2.1. Classes of Program Measurements

Program measurements are an extraction of some of the quantitative attributes from the programs that are executed on a computer. Classes of program measurements vary depending on two factors. One is the form or level of the program from which the measurements are extracted, while the other is the state of the program when the measurements are obtained.

Programs measurements can be obtained at the source and architectural levels. Measurements obtained from the source code supply information about the usage of the features of the programming language, whereas, measurements obtained from the assembly or object code provide information about the usage of the features of the architecture. Source-level measurements can be correlated to architectural-level measurements. Thus, source-level measurements can be used to provide insight for architectural decisions on any machine with a compiler for that programming language. This correlation,

however, is not always obvious. Architectural-level measurements give more precise information about a specific architecture.

Two states of programs in which measurements can be obtained are the static and dynamic states. Static measurements refer to the text of a program and count each statement or machine instruction equally. Dynamic measurements refer to the execution of a program and count each statement or machine instruction by the number of times that it is executed. Static measurements are easier to obtain and guarantee complete coverage of the program. Since each statement or machine instruction in a program is rarely executed the same number of times, static measurements do not give realistic information on performance. The dynamic coverage of the program, however, is driven by the test data. If the test data is not representative of how the program will be used on the machine, then the dynamic measurements are less meaningful.

#### 1.2.2. Methods of Obtaining Program Measurements

There have been several different methods or combination of methods used to collect program measurements. The factors that may influence the choice of a method include:

- 1. implementation effort

- 2. accuracy of measurements

- 3. types of measurements required

- 4. computational requirements for obtaining measurements

Several techniques for collecting program measurements are described below.

*Program simulation* imitates a machine by interpreting the machine instructions [AIW75, BSG77]. Dynamic architectural-level measurements are updated as the simulator interprets each instruction. The efforts to construct a simulator and a compiler are comparable. The total execution time of a simulated program is typically hundreds of times slower than if the program is executed directly [HLT87]. The main advantage of program simulation is its portability. Since a simulator for a specific architecture can be written in a high-level language, it can be executed on any machine that supports that language. Thus, measurements can be obtained for a machine that does not yet exist.

*Program tracing* records a sequence of events which occur during the execution of a program. These events may include the sequence of instructions executed and the memory addresses referenced. Program tracing can be accomplished by several mechanisms and is sometimes available as an option on a machine. One way to implement tracing is to have the machine interrupted after the execution of each instruction [DDD81]. The interrupt handler then invokes a user-defined handler that records the trace information associated with the instruction, which can produce large volumes of output. A filter, a program that reads input data, performs some operation on that input, and writes output data, can process the trace output to obtain the program measurements. The execution of a program with tracing enabled may run 1000 times slower than one without tracing [HLT87]. An advantage of using tracing is the ability to collect dynamic architectural-level measurements that require knowledge of the order of the execution of instructions [Lun77, PeS77, Wie82].

*Program sampling* periodically interrupts a program for a very short interval of time in order to inspect its state. Measurements are collected during each of these intervals. Sampling incurs little overhead since the program being measured is only interrupted for a small percentage of its execution time. Sampling measurements typically vary with different executions of the same program and thus can only be used as estimates of complete dynamic measurements. If the state of the program is sampled more frequently, the accuracy of the measurements improve and the overhead of obtaining measurements increases. Profiling is the dynamic measurement of the frequency or time spent at each place in a specific program. The profiling facility of UNIX uses sampling to estimate the execution time required by each routine in a program [GKM82].

*Program monitoring* collects dynamic architectural-level program measurements without perturbation of a machine. This method is only possible with a hardware device known as a hardware monitor. The frequency and time taken by each instruction can be measured with this method [CIL82]. The advantage of this method is that program measurements can be collected with no overhead in execution time. The disadvantages include limited measurements and the requirement of a specialized, expensive, hardware device. *Program analysis*, a simple and fast method, extracts static measurements directly from the text of a program. Filters can easily be constructed by modifying the parser of a compiler or an assembler to obtain the measurements. Since this method just collects static measurements, more realistic information on performance can only be obtained using other methods that collect dynamic measurements [Kat83]. This method has been used to extract static measurements from both source and machine code [Coo89, Dit80, Knu71, SwS82].

*Program instrumentation* modifies a program to increment counters during execution. Static information, collected by program analysis, is associated with each counter. After the termination of the execution of the program, each set of static information is weighted by the value of its associated counter to produce the dynamic measurements. This method has been used to modify the source code of a program to obtain dynamic source-level measurements [Knu71]. It has also been used to modify assembly or machine code to obtain both dynamic source-level measurements, if optimizations are not applied across source-level statement boundaries [Tan78], and dynamic architectural-level measurements [HLT87]. Modification of programs has been accomplished through the use of filters or as an option in compilation. Since a basic block has only one entry and one exit point, the instructions within a basic block are always executed the same number of times. Counting the number of times that each basic block is executed to measure the frequency of executed instructions was proposed by Weinberger [Wei84]. Modification captures program measurements with little overhead in execution time. One must ensure, however, that the modifications made to collect measurements do not change the execution behavior of the program.

An emulator has been defined to be a complete set of microprograms which, when embedded in a control store, define a machine [Ros69]. *Emulator instrumentation* modifies the microcode of a machine to update dynamic architectural-level measurements after the execution of each macroinstruction. This method does not require much runtime overhead as compared to tracing or simulation. For example, modification to collect instruction frequency information slowed a Mesa emulator by about a factor of six [McD82]. Another problem is that the microcode of a machine is not always accessible to one desiring to collect program measurements. Even if it can be accessed, microcode is also difficult to modify and maintain which would discourage experimentation.

#### 1.2.3. Applications of Analyzing Program Measurements

Program measurements have been used in architectural applications for the evaluation and modification of existing architectures and the design of new architectures. The effectiveness of instructions and addressing modes has been evaluated by examining the frequency in which they occur [CIL82, Dit80, SwS82, Wie82]. Frequency measurements can be used with timing information to provide a more accurate estimate of the influence of an instruction or addressing mode on the performance of a machine [PeS77]. Frequency of occurrence of instructions and addressing modes has also been used as the criteria for encoding instructions [CoD82, Tan78]. Traces of addresses have been used for cache and paging design [Win73]. Evaluating dynamic sequences of instructions has been used to propose new instructions, guide pipeline design, and evaluate instruction buffer size [Lun77, McD82, PeS77, SwS82]. By analyzing program measurements one can use an iterative design method to evaluate the effectiveness of modifications such as adding a new instruction or changing the number of registers.

Program measurements can be used in several applications in the area of compilers. Frequency information can indicate if the compiler is not able to find specific instructions or addressing modes. Measurements indicating the costs of operations and operands can aid in the evaluation of different compilers. These measurements can also help the compiler writer evaluate the effectiveness of different optimizations. Measurements of the frequency spent at each place in a program have been redirected as input to the compiler as an aid in compiler optimization [CNO87].

#### 1.2.4. Previous Studies Using Program Measurements

There have been many studies involving program measurements. These studies have varied in many aspects including the set of benchmark programs used, types of measurements obtained, and method of data collection.

#### 1.2.4.1. Studies Using Source-Level Program Measurements

Knuth performed one of the earliest and most influential studies of source-level program measurements [Knu71]. He took static source-level measurements of 440 FORTRAN programs and dynamic source-level measurements of twenty-four FORTRAN programs. The static measurements were collected by program analysis and the dynamic measurements were collected by program instrumentation of the source code. Both the static and dynamic measurements were used to analyze FORTRAN language feature usage. By examining the static measurements Knuth discovered that most assignment statements were very simple. He found that 68% of assignment statements had no operators on the right-hand side and 17.5% had only one operator. Of those assignments with one or more operators, 39% had the same variable being assigned the value of the expression as the first operand in the expression. Knuth also discovered that 58% of static variable references were simple scalars. Analysis of the dynamic measurements showed that 67% of all statements executed were assignment statements. Since a large percentage of the assignment statements had no operators on the right-hand side, this result implies that special attention should be given simple data movement instructions on a machine.

Alexander and Wortman [AIW75] collected static and dynamic source-level measurements from ten XPL programs on a IBM/360. Program analysis was used to collect the static measurements by modifying the compiler to count the number of times that each feature of the language was used. Using the static measurements and interpretive execution they were able to produce the dynamic measurements. The measurements collected were used to analyze XPL language feature usage. Analysis of dynamic measurements revealed that 42% of the XPL statements executed were assignment statements, 13% were conditional statements, and 13% were call statements. This showed that a large percentage of instructions dealt with moving data and that transfers of control occurred frequently. They discovered that 72% of compiler productions applied were used to parse expressions as opposed to parsing other constructs in the XPL language. As a result of this finding, several compiler writers use a different technique for parsing expressions to increase the speed of compilation [Flo63, Han85]. Alexander and Wortman also used the measurements to analyze the IBM/360 instruction set. They discovered that 56% of all numeric constants could be represented in four bits and that the branch destination of over half the branching instructions executed was no more than 128 bytes distant. These observations imply that short forms of constants and branch address destinations may be effective for reducing the average size of an instruction.

Tanenbaum [Tan78] collected static and dynamic source-level measurements from more than 300 procedures written in SAL on a PDP-11/45. Program analysis was used to collect static measurements by

modifying the compiler to count the number of times each feature of the source language appeared in the program. The collection of dynamic measurements was accomplished using program instrumentation by modifying the compiler to insert instructions in the object code. Using the measurements he analyzed the use of language features in SAL. He discovered that 41.9% of statements executed were assignment statements, 36% were if statements, and 12.4% were call statements. Of the assignment statements executed, 19.2% stored a constant and 66.3% had no operator on the right side of the assignment. Tanenbaum found that the addition operator accounted for 57.4% of arithmetic operators used and the comparison for equality accounted for 50.6% of relational operators used. Analysis of procedure calls revealed that 72.1% of the calls executed had two or less arguments. The static measurements also showed that there were many simple operations that occurred frequently. Given all other factors as being equal, a smaller program will run faster than a larger one since fewer bits are fetched from memory. A smaller program can also reduce the number of page faults and cache misses in a memory hierarchy. The results from the analysis were used to propose a new instruction set and how the instruction set should be encoded. By encoding the frequently occurring instructions, he reduced program size by a factor of three.

Cook and Lee [CoL82] collected static measurements using program analysis from more than 120,000 lines of Pascal programs. A filter was constructed by modifying a Pascal parser to collect these measurements in twelve different contexts. The contexts included procedures, functions, various control statements, conditional expressions, left and right sides of assignment statements, and argument lists. They discovered that less than 12% of subprograms were nested inside other subprograms. Analysis of the measurements also revealed that global variables in enclosing procedures were referenced infrequently. These results showed that implementing an expensive mechanism to perform up-level frame addressing efficiently would not be worthwhile. An investigation of argument passing indicated that 84% of all procedures had fewer than four local variables, 97% had fewer than four arguments, and 67% of arguments passed to routines were simple variables and constants. The results of this investigation implies that short forms of displacement addressing modes would be effectively used and the importance of a simple push instruction. Cook and Lee discovered that constants accounted for 34% of all

operands. A large percentage of operands as constants signifies the importance of having an immediate addressing mode. They found that 86% of for loops contained less than eight instructions. A small number of instructions in for loops indicates that the iteration variable of the for loop could be kept in a register since the register could be reused in nonoverlapping for loops and that an instruction buffer may be effective. An examination of the distribution of integer constants revealed that negative constants appeared much less frequently than positive constants. Such a skewed distribution suggests that implementing immediate addressing to allow a symmetric range of negative and positive values may not be worthwhile. Cook and Lee discovered that 66% of array references could be accomplished in a single indexing operation when the index is shifted by the size of an element in the array. Therefore, an aligned indexing addressing mode would be useful. An analysis of assignment statements disclosed that most of the assignments assigned values to simple variables and had no binary operators. This revealed that simple data movement instructions would be used frequently.

#### 1.2.4.2. Studies Using Architectural-Level Measurements

Lunde [Lun77] used forty-one programs written in five different high-level languages in collecting measurements on the DECsystem10. He collected dynamic measurements by analyzing a trace of a program's execution. He used these measurements to determine the number of registers needed for the machine by inspecting the maximum number of registers being used at any point in the program. He found that, in general, he could generate code that was almost as efficient using only eight of the sixteen registers available on the DECsystem-10. He discovered that 75% of the instructions executed were from less than 11% of the possible instructions. This implies that encoding the commonly executed instructions could be effective to reduce the average size of an instruction. Over 40% of the instructions were moves between a register and memory. Almost 30% of the instructions executed were branches. As a result of analyzing these measurements he suggested a need to improve the calling sequence, memory-to-memory moves, type conversions, and loop control. Lunde also used the trace data to determine the most frequently occurring pairs and triples of sequentially executed instructions to suggest new instructions.

Peuto and Shustek [PeS77] collected dynamic measurements using program tracing from seven programs executed on an IBM 370 and AMDAHL 470. They used a trace program to capture the characteristics of each instruction that was executed. An analysis program was implemented as a coroutine to avoid huge trace files. Use of the trace and analysis programs resulted in programs executing 300 times slower than normal. Peuto and Shustek found that between 50% to 60% of branch destinations were within 128 bytes of the branch instruction. This showed the usefulness of program-counter-relative branch instructions. They found that the average number of bytes of instructions executed between successful branches was less than thirty-two bytes. This justifies the choice of thirty-two bytes for the linesize of the cache on both of the machines. They examined pairs of opcodes to suggest new instructions and possible bottlenecks due to pipeline conflicts. Peuto and Shustek analyzed the dynamic data gathered from the trace program to estimate the execution time of the programs on the two machines. They examined the instruction interactions to determine the penalties due to pipeline conflicts. Using the addresses from operands and instructions, they simulated cache memory to determine the penalties of cache misses. They determined the percentage of execution time required by each instruction by using the number of times that an instruction was executed and the estimated speed of the instruction. Peuto and Shustek found that the most frequently executed instructions were often not the ones which accounted for most of the execution time. This showed that frequency counts alone can be misleading when attempting to determine the influence of a specific instruction. The ability to accurately estimate the execution time of a program can also be used to predict the performance effect of a future change in a machine.

The Computer Family Architecture committee [FuB77] established a set of criteria to measure computer architectures. In the CFA architecture evaluations [FSB77], twelve programs were used to evaluate and rank nine different architectures. The influence of specific architectural features was not evaluated. Most of the test programs were small, usually requiring less than 200 static machine instructions. Each test program was hand-coded in the assembly language of each machine. The measurements used in the evaluation included program size, number of memory transfers, and number of register transfers. The method of obtaining most of these measurements was to simulate code that was generated

in an ISP notation [BSG77].

Ditzel [Dit80] performed a static analysis of machine code on the Symbol computer. Using program analysis to collect static measurements of object code generated from five programs written in SPL, he analyzed the instruction frequency, space usage, and jump distances. He found that on the Symbol computer, a stack machine, most of the program space is used by literals and addresses. He discovered that 50% of the jump destinations were within thirty-two words of the jump instruction. He suggested the use of short forms for identifier references, relative jumps, and small constants.

Sweet and Sandman [SwS82] performed a static analysis of Mesa object code. They determined the more frequently occurring types of instruction operands, types of instructions, and pairs and triples of instructions. Using an iterative design method they proposed new instructions and determined the effect of each change. These new instructions were either more compact versions of frequently occurring instructions or combinations of frequently occurring operations. McDaniel [McD82] collected dynamic measurements from two Mesa programs on a Dorado personal computer by microcode instrumentation to measure the frequency of instruction use. He used the measurements for an evaluation that included instruction formatting, the instruction fetch unit, and pipelining requirements. The Mesa studies showed that program measurements are useful for a variety of applications.

Wiecek [Wie82] gathered dynamic measurements of VAX-11 instruction set usage from the execution of six different compilers. She used VAX-11 instruction trace software to trap on each instruction executed to generate the trace data. Programs were then used to analyze instruction frequency, operand specifiers, data memory references, register utilization, instruction sequencing, and branch displacements. The move instruction was the most frequently used instruction and the most frequently used addressing modes were the simpler modes. These modes were register (39.9%), immediate (15.2%), byte displacement (14.2%), and register deferred (7.8%). These results showed that architectures should effectively support simpler instructions and addressing modes. Of the eleven most frequently used instructions, the return and call instructions were the most time consuming. Wiecek also found that there was an average of 3.9 instructions between branches. These observations demonstrate the large influence of calls and branches on the execution of programs. Cook and Donde [CoD82] used the results from a study of Pascal programs [CoL82] as guidelines in designing the instruction set for MCODE, a stack machine. This machine is designed to execute instructions compiled from programs in StarMod, a distributed programming language based on Modula. The StarMod compiler had already been retargeted to the VAX and the PDP-11. They used a "set mode" instruction to control whether arithmetic operators were performed as real or integer operations. They found that the mode of instructions was changed infrequently. Cook and Donde also encoded more compactly the most frequently used instructions. These modifications resulted in an overall reduction in program size. They measured the sizes of thirty programs compiled on the three machines. The VAX code contained over twice the number of bytes required by the code for MCODE and the PDP-11 code required 50% more space.

Clark and Levy [ClL82] used a hardware monitor on the VAX-11/780 to measure the frequency and execution time of each VAX-11 instruction. Only ten instructions represented over 60% of the instructions that were executed. Simple data moves were the most common type of instruction and branches were the second most frequent. This result again showed that the simpler instructions tend to be heavily used. They found that programs compiled from different languages or applications have the potential for using the instruction set differently.

Patterson and Sequin [PaS82, PaP82] collected static and dynamic measurements from eight Pascal and C programs. Patterson used the results of his study and previous studies in the design of the RISC I machine. Since the results showed that the simpler instructions and addressing modes are the most frequently used, he used a reduced instruction set to make the instruction cycle fast. He determined that the register window approach was feasible since most variable references and arguments to functions were scalars and the average calling depth was not very deep. Since branches occurred very frequently in executed instructions, he used a delayed branch technique to avoid pipeline delays. Patterson used the results of this study and the RISC I and RISC II efforts to suggest new computer design principles [Pat85] that stress fast instruction cycle time, simple decoding, pipelined execution, and compiler technology. Huck [Huc83] compared four different architectures using program tracing and emulator instrumentation. The most complex of the architectures was found to execute the fewest instructions while the simplest of the architectures had the fastest execution time per instruction. Performance of the architectures was affected by not only differences in the architectures but also other factors such as differences in compilers. Huck then analyzed the effects of compiler optimization techniques. He discovered that fixed-point computation and memory references were reduced while branching instructions were typically unaffected. This showed that as more compiler optimizations are applied, the percentage of control instruction increases.

Wirth [Wir86] compared three architectures based on code density and simplicity of compilation. The architectures were the National Semiconductor 32000, Motorola 68000, and Lilith. The same front end of a Modula-2 compiler was used for all three machines. The same degree of optimization was used in each back end. Since a stack machine does not have directly addressed registers, optimizations such as allocating variables and arguments to registers were not performed. The Lilith, a stack machine designed for executing compiled Modula programs, generated more total instructions, but required fewer total bytes for the compiled code. The Lilith code generator was also found to be smaller than the compilers for the other two machines. This study showed that code generators for simple stack machines would typically be simpler than machines with complex instruction sets and directly addressable registers. This is due to having fewer instructions that can be selected when generating code and fewer optimizations that can be performed. The study also revealed that compilers for stack machines would typically produce smaller executable programs due mostly to arithmetic instructions having implicit operands on the expression stack.

Cook [Coo89] collected static measurements from Lilith machine instructions that were produced by compiling Modula-2 programs obtained from system software. These programs included the operating system, the Modula-2 compiler, and text editors. The compiled software contained over 146,000 instructions. Most of the instructions on the Lilith are represented in a single byte. These short instructions are partly possible since the Lilith is a stack machine which allows instructions to implicitly reference operands. Other instructions that occur frequently are encoded to save space. Cook found that twenty of the 256 instructions represented 50% of the instructions. This observation suggests that the scheme of encoding a specific subset of the instructions in the instruction set can be effective. He discovered that most operations were performed in types defined by the user rather than predefined types. He studied frequently occurring pairs of instructions to suggest new instructions. He also compared the distribution of instructions on the Lilith to the functionally equivalent set of instructions for the Mesa architecture on the Dorado. The Lilith was designed to support Modula-2 and the Dorado was designed to support Mesa. He found that the differences that occurred in the distribution of instructions between the two machines were due mostly to code generation strategies and language usage.

Adams and Zimmerman [AdZ89] collected dynamic measurements using program tracing from the execution of seven programs on an Intel 8086. Only twenty-five instructions, or 25% of the total 8086 instruction set, were responsible for about 91% of all the instructions executed. This shows that only a fraction of the available instructions are used very frequently. Register to register moves appeared very frequently. This suggests that the specialized use of registers on the 8086 resulted in many registers being shuffled around. Adams and Zimmerman compared their results to previous studies on the VAX-11 [Wie82] and found many of the most frequently used instructions for both machines were the same. This occurred despite the VAX-11 having a much more complex instruction set.

# **CHAPTER 2**

# **METHOD FOR GATHERING DATA**

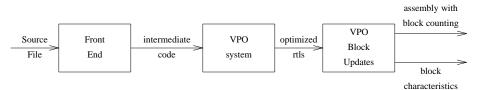

To evaluate an instruction set effectively, one must collect measurements from the program's execution that can be used to evaluate the influence of specific features of the instruction set. As described previously, program instrumentation captures this data for subsequent analysis with little overhead. One way to accomplish program instrumentation efficiently is to modify the back end of the compiler to store the characteristics of the instructions to be executed and to produce code which will count the number of times that each instruction is executed. These modifications have been implemented in a portable optimizer called *vpo* (Very Portable Optimizer) [BeD88] and are described in subsequent sections. The environment that comprises the modified compiler and programs used to produce reports is called *ease* (Environment for Architecture Study and Experimentation) [DaW90a] and is illustrated in Figure 1.

Figure 1: Method for Gathering Data

## 2.1. Instruction Characteristics

The optimizer, *vpo*, replaces the traditional code generator used in many compilers and is retargeted by supplying a description of the target machine, a *yacc* grammar. Instructions are stored as character strings using ISP-like register transfers [BeN71]. For example, the register transfer list (RTL)

$$r[1] = r[1] + r[2]; cc = r[1] + r[2] ? 0;$$

typically represents a register-to-register add on a machine. Though each RTL is machine-specific, the form allows optimization of RTLs to occur in a machine-independent fashion. One optimization per-

formed by the compiler is instruction selection. *Vpo* links instructions that are candidates to be replaced by a more complex instruction that performs the same function. This is accomplished by symbolically simulating pairs and triples of linked instructions to produce a combined effect. The machine description is used as a recognizer to determine if the combined effect is a legal instruction.

The first modification to *vpo* necessary to collect measurements is to have the optimizer save the characteristics of the instructions that will be executed. As an instruction is parsed, information about the characteristics of the instruction is collected and used for semantic checks by *vpo*. The semantic checks are modified to store these characteristics with the RTL by invoking a machine-independent routine. The routine is only invoked if the option for collecting data is set and no semantic errors have occurred. The routine receives the instruction type and the semantic record containing the fields of the instruction. After all optimizations have been completed, most of the instructions have been parsed. Those instructions that have not yet been parsed are then parsed, and their characteristics stored with the instruction. The information about each instruction is then written to a file. An example of a routine that stores information about a Motorola 68020 call instruction is shown in Figure 2.

```

/*

* call - written by compiler writer to check semantics of call instruction

*/

void call(i1)

struct sem_rec *i1;

{

/* if generating assembly code */

if (dassem)

printf("\tjbsr\t%s\n", i1->sem.call.addr->asmb);

/* else if no semantic errors and measurements are to be collected */

else if (!erflag && swm)

stinstinfo(JSBRI, i1);

}

```

Figure 2: Storing Instruction Information

### 2.2. Frequency Counters

The second modification is to have the optimizer generate code after all optimizations have been performed to count the number of times each instruction is executed. Within each function there are groups of instructions, *basic blocks*, that are always executed the same number of times. There are also groups or classes of basic blocks that are executed the same number of times and are denoted as *execution classes*. Thus, the code that the optimizer generates to count the number of times that each instruction in an execution class is executed is inserted in only one basic block in the execution class.

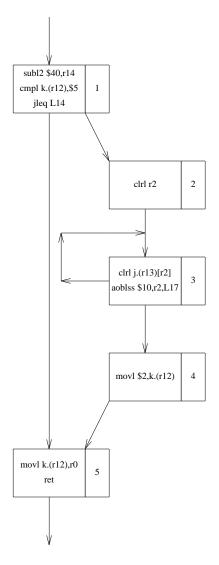

An example of inserting frequency counters is given in Figures 3—6. Figure 3 shows a C function. Figure 4 gives the VAX-11 assembly code that would normally be produced by *vpo* for that function.

Figure 3: C function

```

.text

.globl _foo

foo:

.word 0x0

.set

k.,4

.set

j.,-40

subl2

$40,r14

cmpl

k.(r12),$5

L14

jleq

clrl

r2

clrl

L17:

j.(r13)[r2]

aoblss $10,r2,L17

movl

$2,k.(r12)

movl

k.(r12),r0

L14:

ret

.data

```

Figure 4: Vax Assembly Code for Function in Figure 3

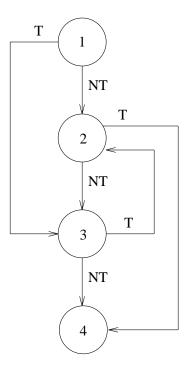

Figure 5 contains the same assembly code broken into basic blocks. Note that although there are five basic blocks there are only three execution classes  $(\{1, 5\}, \{2, 4\}, \{3\})$ .

Figure 5: Assembly Code of Figure 4 in Basic Blocks

Figure 6 shows the modified Vax assembly code with execution class counters inserted. The name of the file being compiled, *test* in this case, is used to distinguish counters from other files in the same executable.

Determining whether a block belongs to an execution class is done in three steps. First, the set of blocks that dominate the current block must be calculated. This information is already available in *vpo* if the option to allocate variables to registers has been set. The second step determines if the current block

```

.text

.globl _foo

_foo:

.word

0 \ge 0

k.,4

.set

.set j.,-40

incl

_test_counts

subl2

$40,r14

k.(r12),$5

cmpl

jleq

L14

incl

(_test_counts + 4)

clrl

r2

L17:

incl

(_test_counts + 8)

clrl

j.(r13)[r2]

aoblss $10,r2,L17

$2,k.(r12)

movl

L14:

k.(r12),r0

movl

ret

.data

```

Figure 6: Vax Assembly Code with Frequency Counters

is always a successor to the dominator blocks. This determines if all paths from one block eventually lead to the current block. The third step checks if the current block is in the same set of loops as the blocks in the execution class. The information for this step is also already available in *vpo*. The algorithms for computing both the dominators of blocks and the blocks in a loop are given in ASU86. Figure 7 presents the algorithm for determining the always successor information.

```

for each block n

set AS(n) to n

while changes to any AS(n)

for each block n

for each block b in AS(n)

for each predecessor p of block b

if all successors of p are in AS(n)

add AS(p) to AS(n)

```

Figure 7: Calculating Always Successor Information for each Block

Figure 8 shows the dominators (DOM), always successors (AS), and execution classes (EC) for the set of

blocks in Figure 5.

### $EC = (DOM \cap AS) - DIFFLOOPS$

| } AS(1)       | =                                         | {1}                                         | EC(1)                                                | =                                                                                               | $\{1\}$                                                                                               |

|---------------|-------------------------------------------|---------------------------------------------|------------------------------------------------------|-------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

| , 2 } AS(2)   | =                                         | {2}                                         | EC(2)                                                | =                                                                                               | {2}                                                                                                   |

| ,2,3} AS(3)   | =                                         | {2,3}                                       | EC(3)                                                | =                                                                                               | {3}                                                                                                   |

| ,2,3,4} AS(4) | =                                         | {2,3,4}                                     | EC(4)                                                | =                                                                                               | $\{2,4\}$                                                                                             |

| ,5} AS(5)     | =                                         | {1,2,3,4,5}                                 | EC(5)                                                | =                                                                                               | $\{1,5\}$                                                                                             |

|               | ,2} AS(2)<br>,2,3} AS(3)<br>,2,3,4} AS(4) | AS(2) =<br>,2,3} AS(3) =<br>,2,3,4} AS(4) = | $\begin{array}{llllllllllllllllllllllllllllllllllll$ | $2$ $AS(2) = \{2\}$ $EC(2)$ $2,3$ $AS(3) = \{2,3\}$ $EC(3)$ $2,3,4$ $AS(4) = \{2,3,4\}$ $EC(4)$ | $2$ $AS(2) = \{2\}$ $EC(2) =$ $2,3$ $AS(3) = \{2,3\}$ $EC(3) =$ $2,3,4$ $AS(4) = \{2,3,4\}$ $EC(4) =$ |

Figure 8: Example of Execution Classes

#### 2.3. Other Modifications

Another measurement needed is instruction size information that is calculated using the assembler on each machine. Labels are inserted before and after each basic block. The difference between the label at the end of the block and the label at the beginning of the block represents the number of bytes of the instructions in the basic block. The size of each basic block in the execution class are then added together. Figure 9 shows the VAX-11 assembly code from Figure 6 with labels inserted to determine the size of each execution class. Each element of the sizes array contains the number of bytes in an execution class.

Some types of measurements require additional code to be generated. For instance, the number of times that conditional branches are taken can be accurately measured by inserting code after each conditional branch to count the number of times each conditional branch was not taken. This count can then be subtracted from the number of times that conditional branches are executed to produce the desired measurement. At first glance, it may appear that one can use the frequency counts from the execution classes to determine this information. With frequency counts alone, however, one cannot produce an accurate measurement with unstructured code. For example, Figure 10 shows two execution paths that may be taken thru a set of basic blocks that would produce identical frequency counts. In the first path three conditional branches are not taken, while in the second the three conditional branches are taken.

```

.text

.globl _foo

_foo:

.word 0x0

.set k.,4

.set j.,-40

incl

_test_counts

LS1_1:

subl2 $40,r14

cmpl

k.(r12),$5

jleq

L14

LE1_1:

incl (_test_counts + 4)

LS1_2:

clrl r2

LE1_2:

L17:

incl

(_test_counts + 8)

LS1_3:

clrl

j.(r13)[r2]

aoblss $10,r2,L17

LE1_3:

LS1_4:

movl $2,k.(r12)

LE1_4:

L14:

LS1_5:

movl k.(r12),r0

ret

LE1_5:

.data

.globl _test_sizes

_test_sizes:

.long LE1_1-LS1_1+LE1_5-LS1_5

.long LE1_2-LS1_2+LE1_4-LS1_4

.long LE1_3-LS1_3

```

Figure 9: Vax Assembly Code with Labels for Size Information

Path1: 1 => 2 => 3 => 4

Path2: 1 => 3 => 2 => 4

Figure 10: Measuring When Conditional Branches Are Taken

Other measurements, such as a trace of addresses of instructions or frequencies of pairs of instructions, require knowledge of the sequence of blocks that are executed. For these types of measurements a routine written in a high-level language can be invoked at the beginning of each basic block with the current block number accessible.

In the past, some instructions in a *vpo* back-end were generated by the code expander in assembly language if optimizations could not affect it. Every type of instruction that is executed must now be represented as an RTL recognizable by the machine description, however, if its execution characteristics are to be collected.

Depending upon the type of measurements required, special cases may be necessary. For instance, the VAX-11 movc instruction moves a variable number of bytes of memory depending upon a value in an operand. To be able to accurately count the number of memory references made by the execution of the instruction, the value of the operand is stored with the other characteristics of the instruction. These special cases only occur when the compiler writer is unable to accurately represent the effects an instruction in the machine description.

## 2.4. Processing the Collected Data

The data that is collected is stored and then analyzed at a later time. Separating the collection and analysis of measurements has a number of advantages. If different evaluations of the data are required, then collection of the data is required only once. If analysis of the execution of several different programs is needed, then the data can be collected from each program's execution separately. Finally, the analysis of the data is separated from the generation of the data and thus requires fewer modifications to the back end of the compiler.

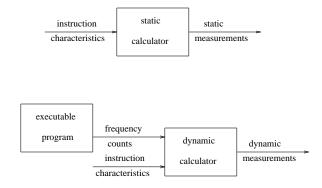

At the end of the execution of a program, the number of times that each execution class is executed is written to a file. The execution counts and the characteristics of the instructions will then both be used to produce the dynamic measurements. The instruction characteristics can also be used to produce the static measurements. Figure 11 shows how both static and dynamic measurements can be obtained.

Figure 11: Producing Reports

If the basic block structures for a program are the same on different machines, then the frequency counts of the execution classes should also be identical. The only reason for executing the program on a different machine in this situation is to ensure that the code generated for the program executes correctly. The basic block structures for a program on different machines, however, may often vary. Code generation strategies, such as either returning from several points in a function or always branching to one location to return, can affect the block structure. Special instructions, such as the move instruction on the VAX-11 to accomplish structure assignments that would otherwise require a loop, can also change the number and structure of basic blocks. Since there is little execution overhead to obtain the frequency counts, it is simpler to execute the program on each machine instead of trying to first determine if the basic block structures are identical.

### 2.5. Discussion

The *vpo* optimizer for ten different machines, already ported and tested, was modified to collect measurements as specified in the previous sections. It typically took three or four hours for an experienced person to make the machine-dependent modifications for the compiler on each machine. For the resulting compiled programs, there is little overhead for collecting data to produce the proposed measurements. For instance, on the VAX-11 the C benchmarks whetstone and dhrystone were executed with and without data collection. The two benchmarks executed with data collection code inserted required only 6% and 13% respectively more execution time than they required without data collection

instructions. The number of counters needed for whetstone was fifty-one. When execution classes were not used and counters were placed in each basic block, whetstone would have required eighty-four counters and 9% more execution time.

The generation of reports from the measurements is also mostly machine-independent. Most of the code from a 500 line C program that produces several different reports has remained unchanged when implemented on the different machines. These reports gather data on the following:

- 1. instruction type distribution

- 2. addressing mode distribution

- 3. memory reference size distribution

- 4. register usage

- 5. condition code usage

- 6. conditional branches taken

- 7. data type distribution

# **CHAPTER 3**

# **ARCHITECTURAL STUDY**

Past architectural studies have suffered from many limitations. Some used a small set of benchmark programs due to the difficulty of collecting data. For instance, in the CFA architecture evaluations [FSB77], twelve assembly language programs were used to evaluate and rank nine different architectures. Most of these programs were less than 200 static machine instructions in length.

Many studies that compare architectures do not account for differences in how the machine instructions are produced. Each test program in the CFA architectural evaluations was hand-coded in the assembly language of the machine to test a specific feature of an architecture [FuB77]. Thus, the quality of the test programs depended upon the skill of the programmer and his knowledge of the machine. Johnson's Portable C Compiler (*pcc*) [Joh79] was retargeted to each machine in Patterson's study [PaP82]. Thus, Patterson claimed that the different compilers in his study used the same compiler technology. The quality of the code produced by each *pcc* compiler, however, depends on the skill of the compiler writer when constructing tables for code generation and the patterns for peephole optimization.

The methods used to accomplish several of the past architectural studies made it difficult to capture certain kinds of information and perform various experiments. Data was collected from machine instructions in many studies without modifying the compiler. The methods used included simulation [BSG77], trace software [Lun77, PeS77, Wie82], and hardware monitors [ClL82]. Capturing specific types of measurements, such as the number of registers used only as temporaries, is not possible with these methods. Furthermore, determining the usefulness of proposed architectural features is difficult without the ability to modify the compiler and obtain information showing how frequently the proposed features are used.

*Ease* has eliminated problems that have limited some past architectural studies. Using *ease* to collect data, one can use a number of realistic programs and collect the data in a timely fashion. For example, on the VAX-11/8600, measurements were collected from the execution of almost 100 million

instructions in less than ten minutes. Properties of *vpo*, the optimizer used in *ease*, eliminate several problems. Since code to perform instruction selection and most optimizations is constructed automatically, the quality of the code generated by *vpo* for each of the architectures has less dependence on the skill of the implementors than compilers using other techniques [DaW89]. For example, tables are constructed by the implementor of a *pcc* compiler to recognize the different instances of trees from which an instruction can be generated. Instructions for *vpo*, however, only have to be represented correctly by the machine description. Retargeting the compiler to a new machine only requires expanding the intermediate language statements to RTLs and describing the architecture. Ad hoc case analysis is unnecessary. Thus, the programs compiled for each of the architectures receive the same degree of optimization. Because an effort was made to separate the machine-independent code from the machine-dependent code to facilitate the retargeting of *vpo*, changing the compiler to implement proposed architectural changes such as reducing the number of registers available, changing the calling sequence, or eliminating an instruction or additional registers usually can be done easily since one RTL can be translated to one or more machine language instructions.

The following sections describe a study of several architectures that involved collecting measurements from the execution of the same set of test programs on each machine. First, the type of measurements extracted by *ease* from each architecture is given. Next, the characteristics of each of the architectures in the study is described. The set of test programs used in the study is then specified. Finally, the measurements obtained from the architectures are analyzed.

## 3.1. Types of Measurements

There are several kinds of data that can be collected to aid in the design, modification, or evaluation of an instruction set. The following is a list of some of the data that has been collected both statically and dynamically using the modified version of *vpo*.

- 1. total number of instructions

- 2. number of each type of instruction

- 3. instruction size information

- 4. number of each type of addressing mode used

- 5. number of memory references

- 6. number of each different size of memory reference

- 7. number of each different memory reference addressing mode

- 8. condition code usage

- 9. distribution of size of data for each instruction

- 10. distribution of addressing modes for each field in each type of instruction

- 11. number of each type of register saved and restored

- 12. register usage

Dynamic data has been collected on the number of conditional branches taken and not taken and the number of instructions executed between branches.

These measurements can be used in a variety of ways. The frequency information can be used to evaluate the usefulness of specific types of instructions, addressing modes, or other architectural features. It can also be used to help determine how the instructions should best be encoded. The total number of instructions and memory references can help to evaluate the effect of changing a specific feature of the architecture.

#### **3.2.** Architectures Studied

The architectural study includes the following architectures:

DEC VAX-11 1. 2. Harris HCX-9 AT&T 3B15 3. 4. Motorola 68020/68881 5. National Semiconductor 32016 Intel 80386/80387 6. 7. Concurrent 3230 8. **IBM RT/PC** 9. Intergraph Clipper SUN SPARC 10.

These architectures differ in a number of ways including the number and complexity of instructions and addressing modes, the number and use of registers, and degree of orthogonality of the instructions and addressing modes. The following subsections describe the code that *vpo* generates and features of the architectures for each machine in the study. The definition of calling sequence conventions, often

influenced by the available instructions or mechanisms in the architecture, can also affect the code that is generated. The calling conventions as defined on the machines were used since the source files of the run-time library on most of the machines in the study were not accessible.

### 3.2.1. VAX-11

The VAX-11/780 has an 8K byte cache used to store data and instructions. There are twelve userallocable registers. There are six scratch registers and six non-scratch registers. Doubles are referenced in pairs of registers.

The instruction set for the VAX-11 is considered complex and very orthogonal. The *vpo* compiler for the VAX-11 can generate fifty-three different instructions and twenty-two different addressing modes for instruction operands without regard to datatype. Most arithmetic instructions allow a two-address (one source and a source that is the same as the destination) or three-address format (two sources and a destination). The supported data types are:

| 1. BYTE   | (8 bits)  |

|-----------|-----------|

| 2. WORD   | (16 bits) |

| 3. LONG   | (32 bits) |

| 4. FLOAT  | (32 bits) |

| 5. DOUBLE | (64 bits) |

| 6. QUAD   | (64 bits) |

A callee-save calling sequence is used (the function that is called has the responsibility of saving and restoring registers that are used).

## 3.2.2. Harris HCX-9

The HCX has an 16K byte data cache as well as an instruction cache that can store up to 4K decoded instructions. Of the thirteen user-allocable registers, two are scratch registers and eleven are non-scratch registers. Doubles are referenced in pairs of registers. There is also one floating-point accumulator which is used by all floating-point operations. The clock period is 100 nsecs and there is a three stage pipeline.

The fixed-point portion of the instruction set for the HCX is very similar to the VAX-11. The compiler for the HCX can generate fifty-four different instructions and twenty-two different addressing modes for instruction operands without regard to datatype. Most integer arithmetic instructions allow a two-address or three-address format. Floating point operations are accomplished in a one-address format (implicit accumulator). The supported data types are:

| (8 bits)  |

|-----------|

| (16 bits) |

| (32 bits) |

| (32 bits) |

| (64 bits) |

| (64 bits) |

|           |

A callee-save calling sequence is used.

# 3.2.3. AT&T 3B15

The AT&T 3B15 has twelve allocable registers, nine general-purpose (fixed-point) and three floating-point. Three of the general-purpose registers are scratch and all three of the floating-point registers are scratch. Each floating-point register can contain a single or double-precision value.

The instruction set for the 3B15 is very similar to the VAX. The compiler implemented for the 3B15 can generate fifty-five different instructions and eleven different addressing modes for instruction operands without regard to datatype. As in the VAX-11, most arithmetic instructions allow a two-address or three-address format. Unlike the VAX-11, there are no indexed addressing modes. The supported data types are:

| 1. BYTE   | (8 bits)  |

|-----------|-----------|

| 2. HALF   | (16 bits) |

| 3. WORD   | (32 bits) |

| 4. FLOAT  | (32 bits) |

| 5. DOUBLE | (64 bits) |

|           |           |

A callee-save calling sequence is used.

AT&T has designed several machines based on the 3B architecture. There are also a few differences in the set of instructions for some of these machines in this family. AT&T defined a set of machine-independent instructions, the IS25 Instruction Set, to allow assembly programs to be portable between each of the machines. Only machine-independent instructions within the 3B family were generated by *vpo* due to portability considerations and lack of documentation on machine-dependent instructions. In some cases machine-independent instructions are expanded by the assembler into several machine-dependent instructions.

#### 3.2.4. Motorola 68020/68881

There are different versions of the 68020 and 68881 floating-point coprocessor for the SUN-3/60 available from Motorola. For these experiments the 68020 has a 256 byte on-chip instruction cache. The twenty-two user-allocable registers are separated into three classes to save bits in the instruction format. There are eight data (integer) registers, eight floating-point registers, and six address registers. Each of these classes has two scratch registers. Floating-point registers can contain either single or double-precision values.

The instruction set for the 68020 is moderately complex and unorthogonal. For example, the only immediate values allowed for the shift instruction is between 1 and 8. Many instructions do not allow operands to reference memory or specific addressing modes. These types of restrictions are to allow tighter encoding of instructions and less use of area on the chip. The *vpo* compiler for the 68020 can generate forty-five different instructions and nineteen different addressing modes for instruction operands without regard to datatype. Arithmetic instructions typically have a two-address format (one source and a source that is the same as the destination). The supported data types are:

| 1. BYTE   | (8 bits)  |

|-----------|-----------|

| 2. WORD   | (16 bits) |

| 3. LONG   | (32 bits) |

| 4. FLOAT  | (32 bits) |

| 5. DOUBLE | (64 bits) |

|           |           |

A callee-save calling sequence is used.

#### 3.2.5. National Semiconductor 32016

The instruction set for the 32016 is considered moderately complex and very orthogonal. The *vpo* compiler for the 32016 can generate forty-seven different instructions and seventeen different addressing modes for instruction operands without regard to datatype. Most arithmetic instructions allow a two-address format. The supported data types are:

| 1. BYTE   | (8 bits)  |

|-----------|-----------|

| 2. WORD   | (16 bits) |

| 3. LONG   | (32 bits) |

| 4. FLOAT  | (32 bits) |

| 5. DOUBLE | (64 bits) |

There are sixteen user-allocable registers divided into two classes, eight integer registers (three scratch) and eight floating-point registers. A callee-save calling sequence is used for integer registers. A caller-save calling sequence, however, is used for floating-point registers (the calling function has the responsibility of saving and restoring registers). Doubles are referenced in even-odd pairs of registers.

# 3.2.6. Intel 80386/80387

The *vpo* optimizer was also ported to the 80386 and 80387 floating-point coprocessor. The fetching and execution of an instruction is implemented in eight different units that operate in parallel. The 80386 integer registers overlap for different datatypes. There are six long (32 bit) registers (three scratch), four word (16 bit) registers, and eight byte (8 bit) registers. In the 80387 there are eight floating-point registers implemented as a stack.

The instruction set for the 80386 is considered unorthogonal. Several operations are required to be performed in specific registers. Typically an instruction can only reference memory with at most one operand. The compiler for the 80386 can generate forty-eight different instructions and fourteen different addressing modes for instruction operands without regard to datatype. Most arithmetic instructions allow a two-address format. The supported data types are:

| 1. BYTE   | (8 bits)  |

|-----------|-----------|

| 2. WORD   | (16 bits) |

| 3. LONG   | (32 bits) |

| 4. FLOAT  | (32 bits) |

| 5. DOUBLE | (64 bits) |

|           |           |

A callee-save calling sequence is used for integer registers and a caller-save calling sequence is used for floating-point registers that are alive across calls.

## **3.2.7.** Concurrent 3230

The compiler implemented for the Concurrent 3230 can generate 101 different instructions and eleven different addressing modes. The large number of different types of instructions was due to mnemonic instruction opcodes being used to depict the type and size of the operands. For instance, the following instructions represent addition operations:

a - add a value from memory to a register

ar - add a register to a register

ai - add a constant to a register

ais - add a 4-bit constant to a register

ah - add a halfword value from memory to a register

am - add a register to memory

ahm - add a register to a halfword of memory

Arithmetic operations are accomplished in a two-address format. The supported data types are:

| 1. | LONG   | (32 bits) |

|----|--------|-----------|

| 2. | FLOAT  | (32 bits) |

| 3. | DOUBLE | (64 bits) |

Whenever a BYTE (8 bits) or WORD (16 bits) is loaded from memory it is converted to a LONG type.

The Concurrent 3230 has sixteen general-purpose registers, eight single-precision floating-point registers, and eight double-precision floating-point registers. A caller-save calling sequence is used.

# 3.2.8. IBM RT/PC

The IBM RT/PC system processor and floating-point accelerator have a reduced set of operations and addressing modes. The compiler implemented for the IBM RT/PC can generate sixty-two different instructions and eight different addressing modes. The instruction opcodes are used to depict the type and size of the operands. For instance, the following instructions represent addition operations:

a - add a register to a register

ai - add a 16-bit constant to a register

ais - add a 4-bit constant to a register

The supported data types are:

| 1. LONG   | (32 bits) |

|-----------|-----------|

| 2. FLOAT  | (32 bits) |

| 3. DOUBLE | (64 bits) |

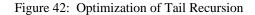

Whenever a BYTE (8 bits) or WORD (16 bits) is loaded from memory it is converted to a LONG type. Memory is only accessed by load and store instructions. All branches have the option of allowing the instruction immediately following the branch to be executed while the instruction at the branch address is being fetched. Multiplication by a register is expanded into sixteen multiplication step instructions. Multiplication by a constant is expanded into a sequence of shift, add, and subtract instructions.

The IBM RT/PC system processor has sixteen general-purpose registers. Only twelve of the sixteen registers can be allocated for general use by the compiler. Four of these registers are scratch and eight are non-scratch.

The system uses an unusual calling sequence. Only one register is used for the functions of both a stack and a frame pointer. The maximum number of longwords passed as arguments to other functions is required to be known to determine the offsets of local variables and temporaries. Up to four longwords are passed in the four scratch registers. If more than four longwords are required then they are passed on the stack. A double-precision or structure argument may have to be partially passed both in registers and the stack.

Immediate operands are limited to sixteen bits for most instructions. Constants requiring more than sixteen bits must either be constructed or loaded from memory in a constant pool. The addresses of any globals that are referenced in the function are also kept in a constant pool. A general-purpose register is dedicated for use as a constant pool pointer.

The floating-point accelerator has sixteen user-allocable registers. Only twelve of the sixteen registers can be allocated for general use by the compiler. Doubles are referenced in even-odd pairs of floating-point registers. All of these registers are scratch. All floating-point instructions are initiated by the system processor by load and store instructions using memory-mapped I/O. A floating-point value that is transferred between a floating-point register or memory must pass through a general-purpose register.

# 3.2.9. Intergraph Clipper

The Intergraph Clipper is considered a reduced instruction set machine. The compiler implemented for the Clipper can generate forty-nine different instructions and nine different addressing modes without regard to datatype. The supported data types are:

| 1. LONG   | (32 bits) |

|-----------|-----------|

| 2. FLOAT  | (32 bits) |

| 3. DOUBLE | (64 bits) |

There are many similarities between the IBM RT/PC and the Clipper. BYTE (8 bits) or WORD (16 bits) values loaded from memory are converted to a LONG type. Memory is only referenced by load or store instructions. Unlike the RT, there are no delayed branches and floating-point instructions are encoded directly into the instruction set.

The Clipper has fifteen general-purpose registers and eight registers that can contain singleprecision or double-precision values. Six of the general-purpose registers and four of the floating-point registers are scratch.

Like the RT, the Clipper has no frame or argument pointer and passes some of the arguments through registers. The Clipper allows arguments to be passed through up to two general-purpose or floating-point registers depending on the argument type. Structure arguments are always passed on the stack.

## 3.2.10. SUN SPARC

The SUN SPARC has a reduced set of operations and addressing modes. The compiler implemented for the SPARC can generate forty-one different instructions and seven different addressing modes without regard to datatype. The supported data types are:

| 1. LONG   | (32 bits) |

|-----------|-----------|

| 2. FLOAT  | (32 bits) |

| 3. DOUBLE | (64 bits) |

As in the other RISC machines in the study, the IBM RT/PC and the Clipper, the SPARC only allows references to memory by load or store instructions (where references to BYTEs (8 bits) or WORDs (16 bits) can be accomplished). The delayed branch for the SPARC has two differences from the delayed branch for the IBM RT/PC. Unlike the SPARC, the RT allows the option of not executing the instruction following the branch for each type of branch instruction. The SPARC instead has an option to not execute the instruction following a conditional branch when the conditional branch is not taken.

The SPARC is the only machine in this study to use register windows. Each of the eight windows has access to four different sets of eight registers listed below.

- 1. global

- 2. output

- 3. local

- 4. input

There are sixteen unique registers in each window where the output registers of one window overlap the input registers of the next window. This overlap allows arguments to passed through the scratch output registers and be received in the non-scratch input registers. The eight non-scratch locals registers are unique to each window while each window can access the same eight scratch global registers. Twenty-seven of the registers that were described are allocable. Two input and two output registers are used for function linkage and one of the global registers always contains a value of zero.

# 3.3. Test Set

Using *ease*, realistic programs can be compiled and executed without excessive delay. The test set used in this study consists of nineteen C programs, forty-five files, and over 23000 lines of source code. For most machines, when the test set is run, over 100 million instructions are executed. At this time only a C front end, *vpcc* [Wat86], has been used with the *vpo* optimizer. Programs written in other high-level languages would provide additional useful information. Since many UNIX systems mainly execute compiled C programs, a set of C programs can still be fairly representative. Table 1 summarizes the test set used in this study. Both the number of lines of code and intermediate code operations [DaW88] are given. The number of lines of code of two identical programs may vary depending upon the comments and style used by the programmers. Since the number of intermediate code operations is not affected by these factors, it may be a more accurate measure for judging the relative sizes of the programs.

| Class                 | Name      | Description or Emphasis             | Lines of Code | Inter Opers |

|-----------------------|-----------|-------------------------------------|---------------|-------------|

|                       | cal       | Calendar Generator                  | 204           | 1341        |

|                       | cb        | C Program Beautifier                | 359           | 2645        |

|                       | compact   | Huffman Coding File Compression     | 420           | 3593        |

|                       | diff      | Differences between Files           | 972           | 8868        |

|                       | grep      | Search for Pattern                  | 532           | 3201        |

|                       | nroff     | Text Formatting Utility             | 6948          | 34627       |

| Unix System Utilities | od        | Octal Dump                          | 894           | 5161        |

|                       | sed       | Stream Editor                       | 1692          | 13571       |

|                       | sort      | Sort or Merge Files                 | 914           | 6564        |

|                       | spline    | Interpolate Smooth Curve            | 338           | 2472        |

|                       | tr        | Translate Characters                | 133           | 1374        |

|                       | wc        | Word Count                          | 104           | 638         |

|                       | dhrystone | Synthetic Benchmark Program         | 731           | 1421        |

|                       | matmult   | Multidimen Arrays and Simple Arith  | 113           | 605         |

| Benchmark Programs    | puzzle    | Recursion and Array Indexing        | 235           | 2586        |