#### FLORIDA STATE UNIVERSITY

#### COLLEGE OF ARTS AND SCIENCE

# TECHNIQUES TO REDUCE DATA CACHE ACCESS ENERGY USAGE AND LOAD DELAY HAZARDS

By

#### MICHAEL STOKES

A Dissertation submitted to the Department of Computer Science in partial fulfillment of the requirements for the degree of Doctor of Philosophy

2019

Copyright © 2019 Michael Stokes. All Rights Reserved.

Michael Stokes defended this dissertation on August 1, 2019. The members of the supervisory committee were:

> David B. Whalley Professor Directing Thesis

Linda DeBrunner University Representative

Xin Yuan Committee Member

Gary Tyson Committee Member

The Graduate School has verified and approved the above-named committee members, and certifies that the dissertation has been approved in accordance with university requirements.

# TABLE OF CONTENTS

| Ał | bstract                                                                                                                                                                                                                                                                                                           | v                                                  |  |  |  |  |  |  |  |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|--|--|--|--|--|--|--|

| 1  | 1 Introduction 1                                                                                                                                                                                                                                                                                                  |                                                    |  |  |  |  |  |  |  |

| 2  | Background         2.1       The Memory Hierarchy         2.2       Anatomy of Memory Access Operations         2.3       Virtually Indexed, Physically Tagged Caches         2.4       Level-Zero Data Caches         2.5       Impact of L1 DC Misses on Processor Performance         2.5.1       Sub-blocking | <b>3</b><br>4<br>5<br>6<br>7<br>7                  |  |  |  |  |  |  |  |

| 3  | <ul> <li>3.2 Memoizing L1 DC and DTLB Information</li></ul>                                                                                                                                                                                                                                                       | 13<br>16<br>18<br>20                               |  |  |  |  |  |  |  |

| 4  | <ul> <li>4.1 Introduction</li></ul>                                                                                                                                                                                                                                                                               | 26<br>28<br>29<br>31<br>33<br>34<br>35<br>37<br>43 |  |  |  |  |  |  |  |

| 5  | Decreasing the Miss Rate and Eliminating the Performance Penalty of a DataFilter Cache5.15.1Introduction5.2Evaluation Environment5.3Lazily Filling Data Words into a DFC Line5.4Decreasing the DFC Miss Rate by Line Sharing and Data Packing                                                                     | <b>48</b><br>48<br>49<br>50<br>55                  |  |  |  |  |  |  |  |

|    | 5.5    | Eliminating the DFC Miss Penalty by Only Accessing DFC Data on Guaranteed Hits | 62        |

|----|--------|--------------------------------------------------------------------------------|-----------|

|    | 5.6    | Related Work                                                                   | 65        |

|    | 5.7    | Conclusions                                                                    | 68        |

| 6  |        | reasing the Miss Rate and the Miss Penalty of a L1 DC                          | <b>69</b> |

|    | 6.1    | Introduction                                                                   |           |

|    | 6.2    | Sharing Words between Multiple L2 Sublines                                     |           |

|    | 6.3    | Compressing and Decompressing L1 DC Data                                       |           |

|    | 6.4    | L1 DC Metaline Fill Policy                                                     |           |

|    | 6.5    | L1 DC Metaline Replacement Policy for Set-Associative Organizations            |           |

|    | 6.6    | Evaluation Environment                                                         |           |

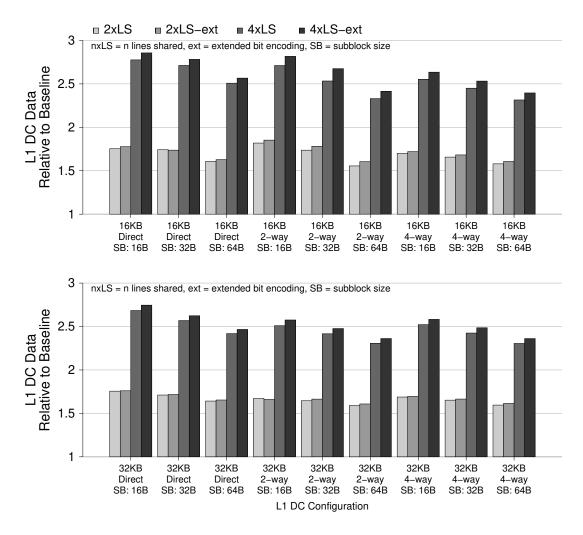

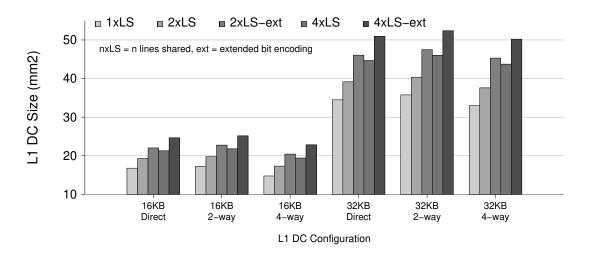

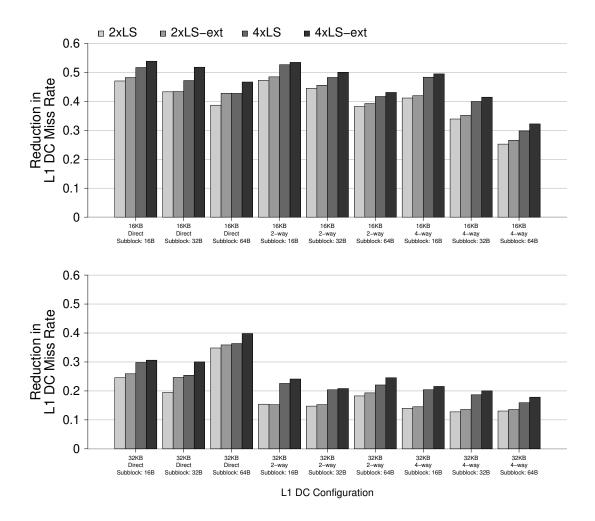

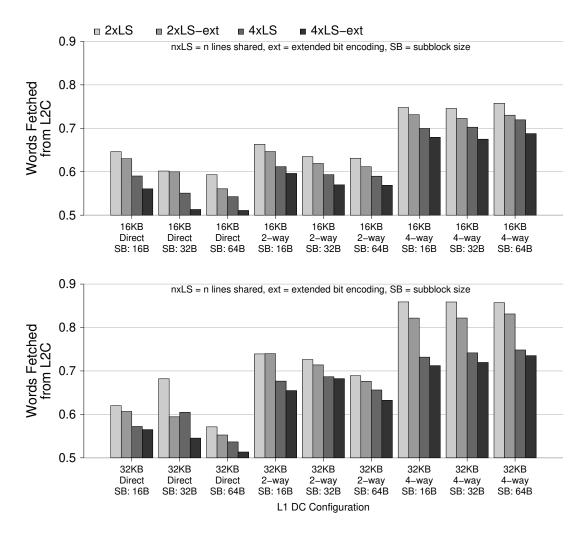

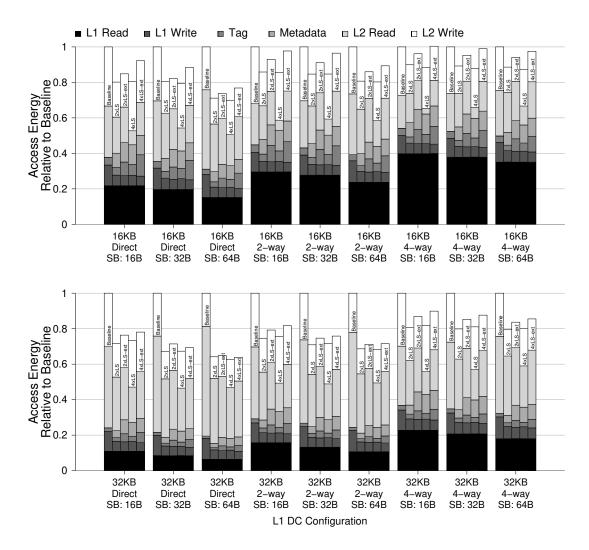

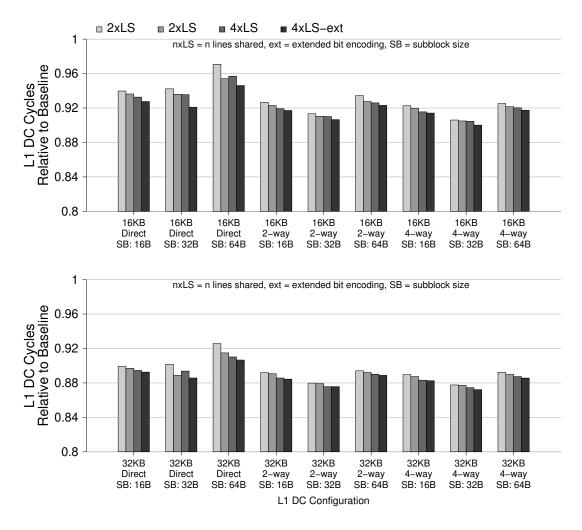

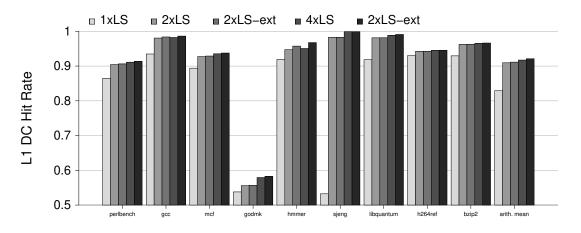

|    | 6.7    | Results                                                                        | 83        |

|    | 6.8    | Related Work                                                                   | 92        |

|    | 6.9    | Future Work                                                                    | 95        |

|    | 6.10   | Conclusions                                                                    | 96        |

| 7  | Con    | clusions                                                                       | 97        |

| Bi | bliogr | aphy                                                                           | 100       |

| Bi | ograp  | hical Sketch                                                                   | 103       |

## ABSTRACT

Level-one data cache (L1 DC) accesses impact energy usage as they frequently occur and use significantly more energy than register file accesses. Modern processors use virtually-indexed, physicallytagged caches to reduce the L1 DC access time at the expense of increasing the energy to access it. It has been estimated that 28% of embedded processor energy is due to data supply [6]. In addition, level-one data caches have a significant impact on performance as a hit in the level-one data cache avoids accessing higher levels of the memory hierarchy, which typically have longer access times. Modern processors employ strategies such as *critical-word first* as well as *lockup-free caches* to limit the penalty of an L1 DC miss. However, as the issue-width of a processor is increased, the number of cycles that can be overlapped with a L1 DC line fill is decreased. This dissertation provides techniques that reduce both the energy usage of level-one data caches as well as improves the performance of processors by reducing the number of stalls due to loads and stores.

## CHAPTER 1

## INTRODUCTION

Level-one data cache (L1 DC) accesses impact energy usage as they frequently occur and use significantly more energy than register file accesses. Level-one data caches are typically set-associative and virtually-indexed, physically-tagged (VIPT). Making a cache set-associative reduces its miss rate while making it VIPT reduces its access time at the expense of increasing the energy required to access it. As the number of transistors placed onto a chip increases according to Moore's Law, the energy expended by simultaneously switching these transistors also increases. As a result, the overall temperature of the chip increases. The processor's clock rate must be constrained to avoid damaging the chip, reducing the chip's power density at the expense of performance, a phenomenon known as the *power wall*. It has been estimated that 28% of embedded processor energy is due to data supply [6]. Thus, reducing data access energy on such processors is a reasonable goal.

In addition, level-one data caches have a significant impact on performance as a hit in the levelone data cache avoids accessing higher levels of the memory hierarchy, which typically have longer access times. Even so, hits in the level-one data cache can still cause *load-delay hazards* when a subsequent instruction demands a value before it can be loaded from the data cache. This problem is exacerbated as modern processors increase the number of cycles required to access the level-one data cache. Modern processors employ strategies such as *critical-word first* as well as *lockup-free caches* to limit the penalty of an L1 DC miss. However, as the issue-width of a processor is increased, the number of cycles that can be overlapped with a L1 DC line fill is decreased.

This dissertation provides techniques that reduce both the energy usage of level-one data caches as well as improves the performance of processors by reducing the number of stalls due to loads and stores. Chapter 3 introduces a non-speculative technique that allows a processor to directly access a set-associative data cache, allowing the processor to 1) avoid accessing the ways of a set that don't hold the data, 2) avoid the DTLB, and 3) avoid the L1 DC tag array. Chapter 4 proposes a technique that not only removes the performance penalty associated with level-zero data caches, but uses level-zero data caches to improve performance by reducing the number of load-delay hazards. In Chapter 5, detailed findings are introduced showing that *word-filled* levelzero data caches are able to save more energy than *line-filled* level-zero data caches. Chapter 5 then provides two methods, *line sharing* and *data packing*, that increase the hit rate of level-zero data caches by significantly increasing the amount of data that can be stored. Chapter 5 goes on to provide a method of utilizing a word-filled, line sharing and data packing level-zero data cache without the performance penalty typically associated with level-zero data caches. Chapter 6 extends the methods shown in Chapter 5 to the level-one data cache. A thorough analysis of line sharing and data packing's effect on various level-one data cache designs is conducted, varying the size, associativity, and the sub-block size, data packing methods, as well as the amount of L2 DC (sub)lines that share an L1 DC line.

### CHAPTER 2

## BACKGROUND

To understand the following dissertation, it's important to know the purpose and functionality of the level-one data cache (L1 DC).

#### 2.1 The Memory Hierarchy

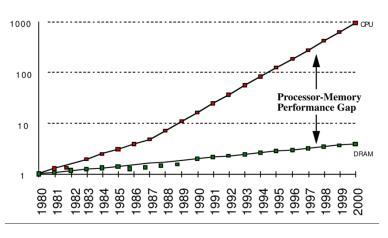

Figure 2.1: The Processor-Memory Performance Gap

Since 1980, processor speeds have increased year-over-year by roughly 60% while DRAM speeds have only increased at a rate of only 7%, a problem known as the processor-memory gap. Processors take advantage of both *temporal locality*, where data that is referenced is likely to be referenced again in the near future, as well as *spatial locality*, where data in proximity to referenced data will likely be referenced as well. To address the processor-memory performance gap, multiple levels of cache are now used. Level-one (L1) caches in the memory hierarchy are large enough to provide reasonable hit rates, but also small enough to provide fast access times. Level-two (L2) and levelthree (L3) caches provide slower access times, but reduce the number of references that need to access main memory. These multiple levels of cache now all reside on the same chip as the processor and are built using SRAM technology. In addition to this, CMOS scaling trends result in faster transistors with with relatively longer wire delays. Because of these reasons, level-one data cache sizes have largely remained the same and are now pipelined to keep up with reduced clock cycle times.

Upon a cache miss, a (sub)line is fetched from higher levels of the memory hierarchy and placed into the cache. Where a cache line can be placed is determined by its *associativity*. In a *fully associative* cache, a (sub)line can be placed in any cache line of a cache. In an *n*-way set associative cache, a cache is split into sets with n cache lines per set and a (sub)line can be placed inside any one of the n ways of a set. A *direct mapped* cache is a special case of a set-associative cache where n is equal to one. By restricting the cache lines where a (sub)line can be placed, both the time and the energy to access the cache decrease at the expense of also decreasing the hit rate.

#### 2.2 Anatomy of Memory Access Operations

Contemporary architectures designed using RISC principles attempt to implement each instruction using a single  $\mu$ op. However, memory operations involve many hidden hardware  $\mu$ ops. These  $\mu$ ops not only form dependence chains, but also use a significant amount of energy.

Conventional Micro Operations

Figure 2.2: Micro-Ops Associated with Load Instructions

Figure 2.2(a) shows code containing a load and a store along with the  $\mu$ ops that implement these instructions. The load  $\mu$ ops are: #1 Add the base register value and the offset to obtain the virtual address (va); #2 Access the data translation lookaside buffer (DTLB) using the va to get the physical address (pa); #3 Perform the tag check to identify the way where the data resides in a set-associative cache; and #4 use the pa index and the way to access the cache data and update the register. Unfortunately, these  $\mu$ ops are not visible to the compiler with conventional ISAs and it would be expensive to implement each  $\mu$ op as an ISA instruction in terms of code size, fetch bandwidth, and energy.

#### 2.3 Virtually Indexed, Physically Tagged Caches

Several hardware techniques shorten this dependence chain and mitigate the delay, but do so at the expense of significantly more energy usage and/or imposed constraints, such as a limited page size. For example, virtually-indexed, physically-tagged (VIPT) caches exploit the fact that the cache index remains invariant during translation with appropriately sized pages, allowing  $\mu$ ops (2), (3), and (4) shown in Figure 2.2(a) to proceed in parallel by simultaneously accessing all ways of data in the L1 DC set at the expense of significant energy usage. This approach leaves the dependence between the first and the remaining three  $\mu$ ops into successive pipeline stages such that the execution unit performs the virtual address computation (i.e.,  $\mu$ op #1) and the memory access stage performs all the remaining operations, leading to the infamous

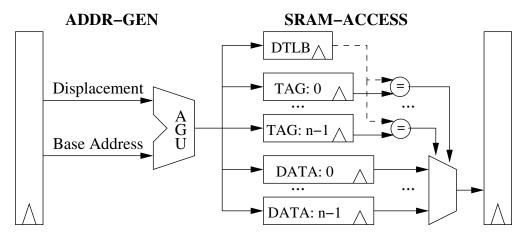

Figure 2.3 depicts how a classical in-order pipeline performs a load from an *n*-way set-associative L1 DC. The virtual memory address is generated by adding a displacement to a base address obtained from the register file in an address generation (ADDR-GEN) stage. The displacement is a sign-extended immediate and the base address is obtained from the register file. In the SRAM-ACCESS stage the DTLB, the L1 DC tags, and the L1 DC data are all accessed in parallel to minimize load hazard stalls and the tag value of the physical address is compared to the tag value of the physical page number from the DTLB.<sup>1</sup> This organization is energy inefficient as all data arrays are accessed, but the value can reside in at most one way within a cache set.

Figure 2.3: Conventional L1 DC Pipeline Load Access

<sup>&</sup>lt;sup>1</sup>The register level after the ADDR-GEN stage is embedded in the DTLB, TAG, and DATA blocks.

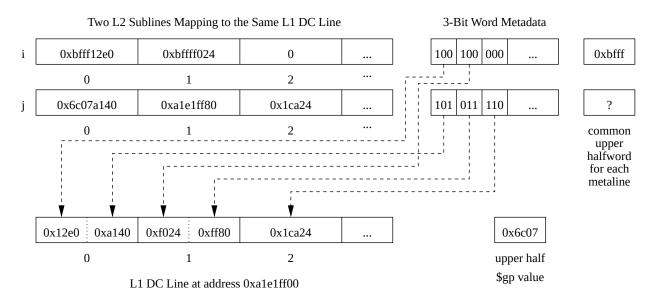

Figure 6.1 shows the address fields used to access the DTLB and the L1 DC. The virtual page number is used to access the DTLB, which produces the corresponding physical page number. The virtual and physical page offsets remain the same. The L1 DC block number uniquely identifies the L1 DC line being accessed. The L1 DC offset indicates the first byte of the data to be accessed in the L1 DC line. The set index is used to access the L1 DC set. The tag contains the remaining bits that are used to verify if the line resides in the L1 DC.<sup>2</sup>

| virtual address          |                                  |        |  |  |  |  |  |

|--------------------------|----------------------------------|--------|--|--|--|--|--|

| virtual page number      | page c                           | offset |  |  |  |  |  |

| DTLB<br>physical address |                                  |        |  |  |  |  |  |

| physical page number     | physical page number page offset |        |  |  |  |  |  |

| L1 DC block numb         | L1 DC                            |        |  |  |  |  |  |

| tag                      | offset                           |        |  |  |  |  |  |

Figure 2.4: Address Fields

#### 2.4 Level-Zero Data Caches

A level-zero data cache (L0 DC), also known as a data filter cache (DFC), has been shown to be effective at reducing data access energy [14,15]. An L0 DC is a smaller, typically direct-mapped cache that is accessed before the L1 DC. A reference that hits in the L0 DC does not need to access the L1 DC while a reference that misses in the L0 DC accesses the L1 DC in the following cycle. An L0 DC is energy efficient since a large fraction of the memory references can be serviced from the L0 DC that is much smaller than a level-one data cache (L1 DC), resulting in less energy usage for each L0 DC reference as compared to an L1 DC reference. However, a conventional L0 DC has disadvantages that has discouraged its adoption in contemporary processors. First, an L0 DC can cause a performance penalty as it has to be accessed before the L1 DC in order to reduce energy usage; upon an L0 DC miss, the L1 DC is accessed a cycle later than it normally would, potentially causing load-delay hazards that would not occur had an L0 DC not been used. This increase in

<sup>&</sup>lt;sup>2</sup>We depict the *physical page number* and the *tag* fields being the same size, but the *physical page number* could be smaller for a virtually-indexed, physically-tagged (VIPT) cache. To simplify the description, we assume these two fields are the same size.

execution time will mitigate some of the energy benefit of using an L0 DC. Second, a single cycle L0 line fill as proposed in many prior studies [7,9,10,14,15,27] has been shown to be unrealistic as it can adversely affect L1 DC area and energy efficiency [3].

#### 2.5 Impact of L1 DC Misses on Processor Performance

L1 DC misses decrease performance as the data must be fetched from higher levels of the memory hierarchy. Higher levels of the memory hierarchy typically take many more cycles to access than the L1 DC. In addition, caches in embedded processors are typically blocking, meaning that memory operations are stalled while an L1 DC line is being filled. One technique mitigates this delay by servicing a load that missed in the L1 DC as quickly as possible by fetching the requested data first. This allows the load to complete faster than if it waited for the entire L1 DC line to be filled. While the remainder of the L1 DC line is being filled, the processor can continue issuing new instructions. However, if a memory-accessing instruction is issued before the L1 DC line is filled, then the pipeline must stall before the line fill is completed. This decreases the latency of an L1 DC miss penalty as well as overlaps the L1 DC line fill with non-memory access operations.

#### 2.5.1 Sub-blocking

One technique embedded processors use to decrease the miss penalty of L1 DCs as well as the energy they consume is to decrease the number of words fetched during an L1 DC line fill. L1 DC lines are split into sub-blocks and line fills occur at the granularity of sub-blocks: when an L1 DC miss occurs, only the sub-block containing the requested word is filled. This means that some sub-blocks of an L1 DC will remain empty as they will not be referenced before the line is evicted. Sub-blocking increases the miss rate as filling an entire L1 DC line captures more spatial locality but decreases the number of words needlessly fetched from higher levels of the memory hierarchy. In addition, it takes fewer cycles to fill a sub-block as fewer words need to be fetched from higher levels of the memory hierarchy.

## CHAPTER 3

# IMPROVING ENERGY EFFICIENCY BY MEMOIZING DATA ACCESS INFORMATION

Level-one data cache (L1 DC) and data translation lookaside buffer (DTLB) accesses impact energy usage as they frequently occur and each L1 DC and DTLB access uses significantly more energy than a register file access. Often, multiple memory operations will reference the same cache line using the same register, such as when iterating through an array. A technique is proposed in this chapter to memoize L1 DC access information, such as the L1 DC data array way and the DTLB way, by associating this information with the register used to access it. When a load or store calculates the effective address by adding the base register with the displacement value, the processor detects whether the effective address shares the cache line memoized with the base register. If so, the L1 DC tag array access and the DTLB access to determine the L1 DC way are avoided and instead the memoized information is used. In addition, only a single data array way in a set-associative L1 DC needs to be accessed during a load instruction when the L1 DC way has been memoized. This nonspeculative memoization approach provides existing executables a significant reduction in data access energy usage compared to a conventional cache and provides even greater energy usage reduction after way prediction is applied when memoized information is unavailable.

#### 3.1 Introduction

Level-one data cache and data translation lookaside buffer accesses frequently occur and each of these accesses use significantly more power than a register file access. It has been estimated that 28% of embedded processor energy is due to data supply [6]. Thus, reducing data access energy on such processors is a reasonable goal.

The tag arrays and data arrays of an L1 DC can be accessed in parallel for load instructions to improve the latency of obtaining data from the L1 DC, which is sometimes referred to as a *conventional* cache [19]. The tag arrays are often accessed before the data arrays of level-two (L2) and level-three (L3) caches to reduce energy usage, which is sometimes referred to as a *phased*

| virtual address          |                                  |             |  |  |  |  |  |

|--------------------------|----------------------------------|-------------|--|--|--|--|--|

| virtual page number      | page o                           | page offset |  |  |  |  |  |

| DTLB<br>physical address |                                  |             |  |  |  |  |  |

| physical page number     | physical page number page offset |             |  |  |  |  |  |

| L1 DC block numb         | L1 DC                            |             |  |  |  |  |  |

| tag set index off        |                                  |             |  |  |  |  |  |

Figure 3.1: Address Fields

cache [19]. The advantage of a phased cache is that at most a single data array need be accessed as the result of the tag check will be known when the data in the cache is accessed. However, using a phased L1 DC is often impractical since the reduced energy usage for the phased L1 DC data accesses would be largely offset by the increased energy required for longer execution times.

This dissertation proposes the *Data Cache Access Memoization* (DCAM) technique to retain data access information so that subsequent memory accesses dereferencing the same register can often more efficiently access the L1 DC. These efficient L1 DC accesses are achieved by associating the L1 DC way and DTLB way with the base register of a memory reference. When the processor detects that a subsequent memory reference will reference the same L1 DC line, the processor can use the memoized information to avoid the L1 DC tag check, avoid the DTLB access, and access only a single data array in a set-associative L1 DC organization. When memoization information cannot be utilized for the base register, the default L1 DC access mechanism (e.g. conventional [19] or way prediction [11,22]) can be used.

The contributions of this dissertation are as follows. (1) We show that simple and efficient memoization techniques that associate data access information with the base register being dereferenced can often be utilized without ISA changes to significantly reduce data access energy usage. (2) We provide a simple method that allows the data access information to be restored even after other instructions update the base register value. (3) We show that energy usage can be further reduced when data access information is unavailable for the nonspeculative DCAM approach by applying a speculative approach, such as way prediction.

#### 3.2 Memoizing L1 DC and DTLB Information

The L1 DC way and DTLB way must be stored in a structure to allow reuse of data access information. In fact, a DTLB access and L1 DC tag check will often be redundant since the same line may be accessed again. Figure 3.2(a) shows code for loading from and storing to the same variable. The store can use the same L1 DC way as the load instruction since the value of r6 has not been changed. Figure 3.2(b) shows an example of accessing sequential array locations, where an L1 DC line is likely to be repeatedly accessed.

| r6=;[pam]              | r20=;[pam]           |

|------------------------|----------------------|

| •••                    | L3:r2=M[r20];        |

| =M[r6];                |                      |

| •••                    | r20=r20+4;[pam]      |

| M[r6]=;                | PC=r20!=r21,L3;      |

| (a) Redundant Accesses | (b) Strided Accesses |

|                        | · · · • • •          |

Figure 3.2: Memoization Examples

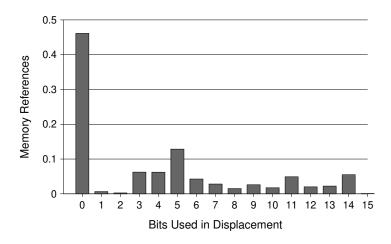

One issue that must be resolved is when the displacement in the load or store instruction is a nonzero value. Figure 3.3 shows the average frequency of the number of bits needed to represent displacement values (the most significant 16 bits are sign extended to be all 0's or 1's) for load and store operations in the MiBench benchmark suite, where the range for n bits is  $-2^{n-1}..2^{n-1}-1$  and does not comprise the values in the previous range. A zero displacement occurs 46% of the time and large offsets comprise a small fraction of the displacements. Note that negative displacements occur less than 2% of the time.

One problem is that the address associated with the base register value may not be associated with the same L1 DC line as the effective address that is computed by adding the base register and the displacement value. For a load or store instruction to be able to use or memoize cache access information, the magnitude of the displacement must be smaller than the L1 DC line size. However, the effective address of a load or store instruction with such a displacement may still fall outside of the cache line associated with the base register. If the displacement is positive and is smaller than the cache line size, then the effective address must point to either the current or next sequential cache line. Thus, the processor tracks both the current and the next sequential L1 DC line associated with the base register, which allows dealing with small positive displacements that cross to the next sequential line in memory.

Figure 3.3: Displacement Size Frequency

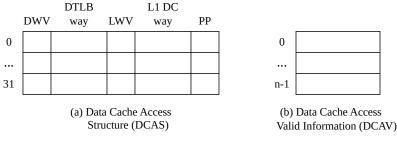

The DCAM approach associates L1 DC access information with the base register number of a load or store instruction and detects when updates to this register does not invalidate this information. Consider the data cache access structure (DCAS) in Figure 3.4(a) that contains fields associated with each base register in load and store instructions. The DWV bit indicates if the DTLB way field is valid. If the DWV bit is not set, then the rest of the DCAS entry is considered invalid. The DTLB way field holds the DTLB way in which the associated physical page number resides. The LWV bit indicates if the L1 DC way field associated with the address in the base register is valid. The L1 DC way field holds the L1 DC way in which the cache line resides that is associated with the address in the register. The LWVN bit indicates if the next sequential line has a valid way. The L1 DC N way holds the way for the next sequential line. The L1 DC set index field (see Figure 3.1) of the effective address indicates the L1 DC set and need not be stored in the DCAS since the set index is available from the effective address calculation. The PP field contains page protection bits from the DTLB entry since the DCAS structure allows DTLB references to be avoided and these bits need to be checked to ensure pages are properly accessed. The DCAS entry needs to be accessed during the EX stage to allow a single L1 DC data array access for a load in the following cycle.

Figure 3.4(b) depicts the DCAV structure used to keep DCAS entries coherent when an L1 DC line is evicted or invalidated. Each DCAV entry contains a bit vector, where each bit represents an integer register. An entry is indexed by the L1 DC way, where n is the L1 DC associativity level.

Figure 3.4: Data Cache Access Information

Each time a DCAS entry shown in Figure 3.4(a) is associated with a line, the bit corresponding to the register number of that way in the DCAV structure is set. Each time a register's LWV bit (see Figure 3.4(a)) is cleared, the bit corresponding to that register number is also cleared in every DCAV entry. When an L1 DC line is replaced or invalidated, the corresponding bits set in the entry accessed by the L1 DC way of that line are used to determine which DCAS entries will have their LWV bit cleared. Thus, this structure contains an inverse mapping between each L1 DC way and the DCAS entries. All the DCAS DWV bits and the values in the DCAV structure are cleared upon a DTLB eviction, which infrequently occurs.

#### 3.3 Detecting DCAS Re-Use

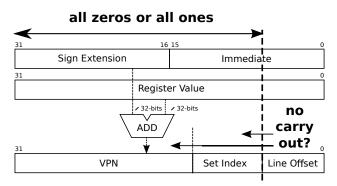

There are many cases where the address in a register is updated, but still is within the same line in the cache and more frequently within the same page. Figure 3.5 shows that it is simple for the processor to detect if the cache line to be accessed will change during an effective address computation of a load or store instruction (M[rs+immed]) or during an integer immediate addition (rd = rs + immed). First, the magnitude of the immediate has to be less than the size of the *line* offset field.

Second, the carry out values can be inspected during the addition to check whether or not the  $L1 \ DC \ block \ number$  as shown in Figure 3.1 has changed. If the set index field is updated during a load or store address computation with a positive displacement that is smaller than the L1 DC line size, then either the  $L1 \ DC \ N \ way$  field can be used or the tag check has to be performed if the LWVN bit is clear. In the latter case, a single way in the DTLB can be accessed using the  $DTLB \ way$  field to obtain the physical tag value when the virtual page number (VPN) field is not updated. If the VPN field is updated, then all the ways in the DTLB have to be accessed. If the set

index field is updated during an integer addition instruction by a small positive value, then the L1 DC way N field is copied to the L1 DC way field and the LWVN bit is cleared. By inspecting the carry out values for integer add or subtract operations using either two register values or register and an immediate, the processor can continue to memoize all or portions of a register's data access information after updates to the base register if the update does not change the cache line or page associated with the address contained in the register.

Figure 3.5: Detecting Address Changes

If an integer add instruction references a source register with its DWV bit set, then its corresponding DCAS information is copied to the destination register DCAS entry if the destination register differs from the source register. Other integer register updates cause the DWV field in the DCAS entry indexed by the destination register number to be invalidated.

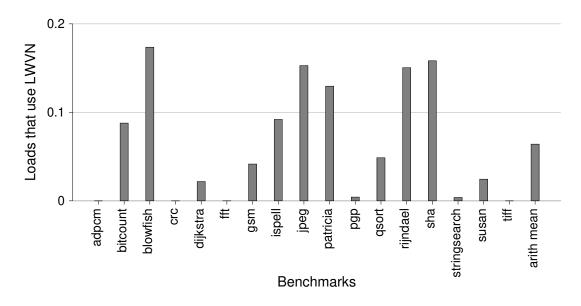

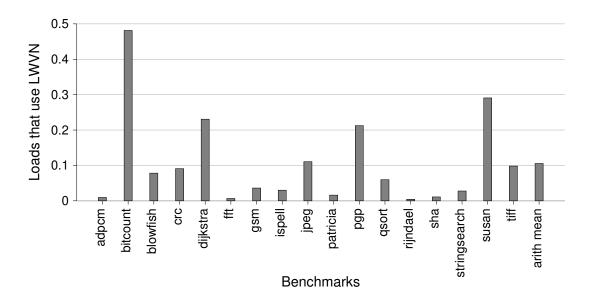

Figure 3.6 shows the percentage reduction of L1 DC tag array and DTLB accesses as a result of using the LWVN field. Benchmarks such as *blowfish* with larger offset sizes than average tend to have a significant improvement. Benchmarks such as *adpcm* saw almost no improvement as virtually all loads and stores used a displacement value of zero.

#### 3.4 The DCAS Refresh Buffer

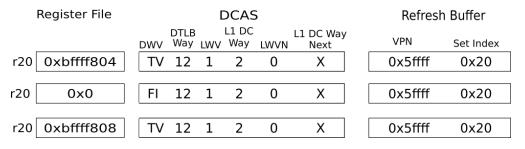

Frequently, a DCAS entry is invalidated but its contents continue to point to the correct cache line. In Figure 3.7 DCAS entry 20 is set during the load instruction and is overwritten during the function call to foo, shown in Figure 3.9(a). During foo's epilogue code, r20's value is restored, again pointing to the same cache line in its DCAS entry. If the processor can detect during a load or a store that the base register's DCAS entry points to the same cache line as the value held inside the base register, then the processor can restore the DCAS entry contents.

Figure 3.6: Reduction of L1 DC Tag and DTLB Accesses Using LWVN

| L3: r2=M[r20];                | foo:sp=sp-12; |

|-------------------------------|---------------|

| jal foo                       | M[sp+4]=r20;  |

|                               | r20=0;        |

| r20=r20+4;<br>PC=r20!=r21,L3; | r20=M[sp+4];  |

| 10120. 121,20,                | sp=sp+12;     |

|                               | jr ra         |

Figure 3.7: DCAS Refresh Example

The processor stores the tag and set index portions of the virtual address of the L1 DC line with a DCAS entry in addition to its L1 DC access information. If a load or store detects that its DCAS entry is invalid but its contents still refer to the cache line associated with the tag and set index stored alongside it, then the processor compares the virtual tag and set index portions of the base register with the virtual tag and set index portions stored alongside the DCAS entry during the EX stage. If they match, then the processor can restore the *DWV*, *DTLB way*, *LWV*, *L1 DC way*, *LWVN*, and *L1 DC way next* fields if they were previously valid. Furthermore, if the DCAS entry and base register don't point to the same cache line but do point to the same page, then the processor can restore the DCAS entry's *DWV* and *DTLB way* fields to avoid a fully associative DTLB access.

DCAS entries can now be in one of three states: 1) valid, meaning the DCAS entry and base register value point to the same cache line and/or page and that the way is known, 2) false invalid, meaning the DCAS entry and base register value may not point to the same line or page but the DCAS information is still valid for the line and page stored in the virtual tag and set index fields of the DCAS entry, and 3) true invalid, meaning the DCAS entry has no valid cache access information.

A DCAS entry becomes valid after a load or a store instruction determines the L1 DC way (DTLB way) and the effective address points to the same line (page) in the base register value. A DCAS entry becomes *true invalid* after an L1 DC line eviction or a DTLB page eviction. A DCAS entry becomes *false invalid* if the base register is overwritten by an instruction that doesn't change its DCAS information. For example, after instruction r20=0; executes in Figure 3.7, the DCAS contents still refers to the same DTLB way and L1 DC way shown in Figure 3.9(b). The DWV field is marked as *false invalid*, indicating that the DCAS cannot guarantee that the base register contents and DCAS entry refer to the same cache line, but it can guarantee that the DCAS entry is still *valid* for the stored tag and set index. The next time a load or store refers to a DCAS entry marked as *false invalid*, the virtual tag and set index fields of the base register are compared with those fields stored in the DCAS Refresh Buffer to see if the DCAS contents can be restored by setting the DWV field to *true valid* as shown in Figure 3.9(c). As the DCAS and the DCAS Refresh Buffer are both indexed by the base register number, the cost of accessing this buffer is relatively inexpensive.

Figure 3.8 shows the percentage reduction in the number of L1 DC tag array and DTLB accesses made when the DCAS refresh buffer is used. On average, this approach reduces the number of L1 DC tag array and DTLB accesses by 10.6%. Benchmarks like bitcount which update a global variable inside of a loop with a function call, and therefore must continually re-load the address, has a significant improvement of over 48%. As the refresh buffer is directly accessed and only used when the DCAM entry is marked as *false invalid*, it will not expend a significant amount of energy, mitigating the energy savings.

Figure 3.8: DCAS Refresh Buffer Effectiveness

Figure 3.9: DCAS Refresh Buffer Example

#### 3.5 Evaluation Framework

In this section the experimental environment is described. The seventeen benchmarks from the MiBench benchmark suite [8], which is a representative set of embedded applications, are used to evaluate the DCAM approach. All benchmarks are simulated using the large dataset option and compiled using gcc with the -03 option.

The ADL simulator [21] was used to simulate both a conventional MIPS processor as the baseline and the modified processor as described in this dissertation. Both configurations are single-issue, in-order processors with six-stage pipelines as shown in Table 3.1. Table 3.2 shows other details regarding the processor configuration utilized in these simulations. Note that the DWV bit is separated from the rest of the DCAS structure so this bit can be accessed during the RF (register fetch) pipeline stage, which allows the processor to avoid accessing the rest of the DCAS structure when the DWV bit is not set.

| Stage | Name         | DCAM Pipeline     |

|-------|--------------|-------------------|

| IF    | Inst. Fetch  |                   |

| ID    | Inst. Decode |                   |

| RF    | Reg. Fetch   | Read DWV Bit      |

| EX    | Execute      | Read/Refresh DCAS |

| MEM   | Mem. Access  | Update DWV/DCAS   |

| WB    | Write Back   |                   |

Table 3.1: DCAM Pipeline Stages

| Table 3.2: Processor Conf | iguration |

|---------------------------|-----------|

|---------------------------|-----------|

| page size           | 8KB                             |

|---------------------|---------------------------------|

|                     | 32KB, 64B line size             |

| L1 DC               | 4-way associative, 1 cycle hit, |

|                     | 10 cycle miss penalty           |

| DTLB                | 32 entries,                     |

|                     | fully associative               |

| DCAS                | 64 total bytes                  |

| DCAS Refresh Buffer | 96 total bytes                  |

| DCAV                | 4 total bytes                   |

Table 3.3: Energy for L1 DC and DTLB Components

| Component                            | Energy               |

|--------------------------------------|----------------------|

| Read L1 DC Tags - All Ways           | 0.494 pJ             |

| Read L1 DC Data - All Ways           | $6.358 \mathrm{~pJ}$ |

| Write L1 DC Data - One Way           | 2.723 pJ             |

| Read L1 DC Data - One Way            | 1.590 pJ             |

| Read DTLB - Fully Associative        | $1.675  {\rm pJ}$    |

| Read DTLB - One Way                  | $0.057 \mathrm{~pJ}$ |

| Read DCAS - 1 Entry                  | 0.025  pJ            |

| Write DCAS - 1 Entry                 | 0.030 pJ             |

| Read DCAV - 32 Bits in All 4 Entries | $0.072 \mathrm{~pJ}$ |

| Write DCAV - 1 Bit in All 4 Entries  | 0.036 pJ             |

| Refresh Buffer Read - 1 Entry        | 0.074 pJ             |

| Refresh Buffer Write - 1 Entry       | 0.142  pJ            |

CACTI was used to estimate L1 DC and DTLB energy usage assuming 22-nm CMOS process technology with low standby power (LSTP) cells. Table 3.3 shows the energy required for accessing

Figure 3.10: L1 DC Data Array Load Accesses

the various components. Leakage energy was gathered assuming a 1 GHZ clock rate.

### 3.6 Results

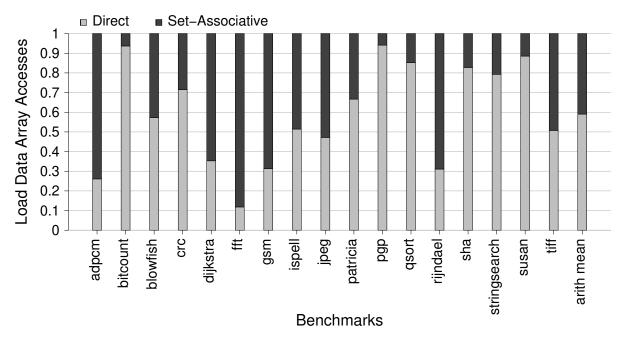

Figure 3.10 shows the ratio of L1 DC data array load accesses that are direct (single L1 DC way) or set associative (all L1 DC ways). Over 59% of the load accesses on average are now direct. In the baseline all loads access all L1 DC data arrays and all stores access a single L1 DC data array as the tag check must occur before the L1 DC is updated.

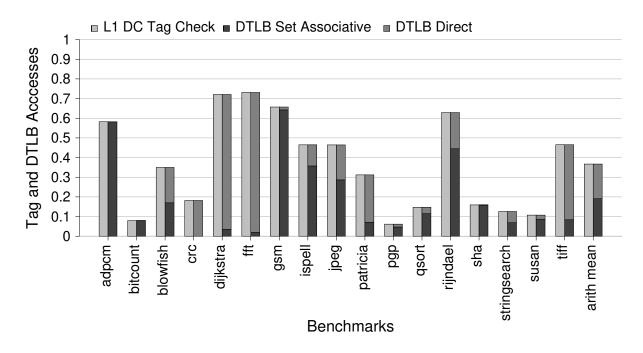

Figure 3.11 shows the ratio of tag checks and DTLB accesses that remain after applying the DCAM technique. On average about 63% of the L1 DC tag checks are eliminated and about 82% of the fully associative DTLB accesses are eliminated. About 18% of the original DTLB accesses are now just accessing a single way of the DTLB, which occurs when the *set index* field is updated and causes an L1 DC tag check, but the *virtual page number* field is unaffected. A single way DTLB access requires much less energy than a fully associative DTLB access, as shown in Table 3.3. On average over 7% of these avoided L1 DC tag checks are due to memoizing the next sequential line.

Figure 3.11: Remaining DTLB and Tag Checks

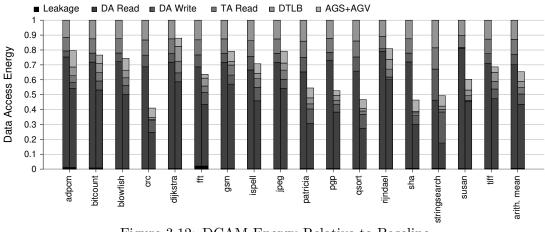

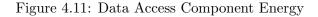

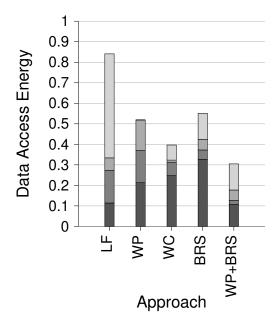

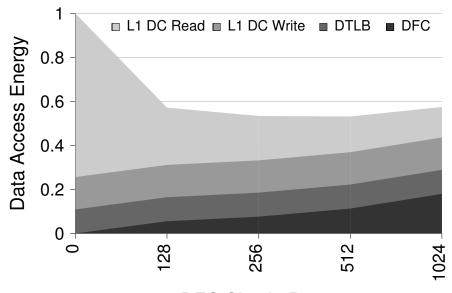

Figure 3.12 shows the breakdown of energy used by the components involved in a data access operation. For each benchmark the left bar shows results for the baseline and the right bar shows results for the DCAM technique. On average about 1.1% of the total energy is due to leakage. For the average baseline data access energy, 57.9% is due to data array reads from load instructions, 12.5% is due to data array writes from store instructions, 6.7% is due to L1 DC tag checks, and 22.7% is due to DTLB accesses. DCAM reduces the energy on average for data array reads to 31.6%, L1 DC tag checks to 2.4%, and DTLB accesses to 4.2%. Note that the energy for data array writes remains the same as writes are direct accesses in both the baseline and DCAM. There is an average overhead of 1.5% for accessing the DCAS and DCAV structures when using the DCAM technique. Overall, the data access energy is reduced to roughly 54% of the baseline on average. The overall energy savings ranges from 71.4% for the *susan* benchmark to 12% for the *fft* benchmark. These energy reductions are significant given that these benefits are obtained on existing binaries with no ISA changes.

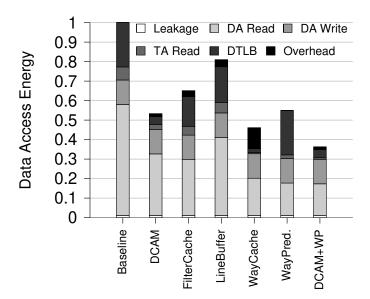

Figure 3.13 shows the same breakdown of energy used by the components involved in a data access operation for other various techniques. Using DCAM alone (52.4%) fails to do better than

Figure 3.12: DCAM Energy Relative to Baseline

way caching (46.1%). Way prediction [11,22] is more commonly used than way caching due to other way caching disadvantages. DCAM (a nonspeculative technique) in combination with way prediction, which only predicts the way when it is not memoized by DCAM, achieves the best results (36.3%). This is because way prediction and other speculative techniques, cannot avoid accessing the DTLB and the tag array. Other techniques that can avoid these accesses do so at a significantly higher cost in overhead energy relative to DCAM, such as way caching. All of the other evaluated techniques have some disadvantages that are described in Section 3.7.

### 3.7 Related Work

Many techniques have been investigated to reduce data access energy. Most of these techniques require trade-offs that may affect how they can be implemented or used. Not all of these techniques conflict with the DCAM approach, as combining some approaches with DCAM could result in lower data access energy than using either approach alone. Taken together, these various characteristics provide a taxonomy of data access efficiency techniques that can be used to compare against the DCAM approach that is shown in Table 3.4.

Unlike the DCAM approach, way-prediction techniques (WP) can have a performance penalty of several percent [11, 22] (OM). These techniques predict which way of the data array is being accessed and this prediction is then verified by performing a L1 DC tag comparison and DTLB access (TD). Newer versions of way-prediction are more accurate, but require a custom SRAM implementation to mitigate the latency of accessing way prediction information before the regular

Figure 3.13: Comparison of Energy Techniques

L1 DC tag and data access (CS) using a hash of the virtual address. Nicolaescu et al. propose to save the L1 DC way of the last 16 cache accesses in a table (WC), and each memory access speculatively performs a fully associative tag search on this table (CP, CS). If there is a match, then only the corresponding way is activated [20]. In contrast, the structures used in the DCAM approach to avoid an associative L1 DC data array access are much less expensive to access. Way halting (WH) is another method for reducing the number of tag comparisons [31], where partial tags are stored in a fully associative memory (the halt tag array) with as many ways as there are sets in the cache. In parallel with decoding the word line address the partial tag is searched in the halt tag array. Only for the set where a partial tag match is detected can the word line be enabled by the word line decoder. This halts access to ways that cannot contain the data as determined by the partial tag comparison. Way halting requires a specialized SRAM implementation that might have a negative impact on the maximum operational frequency (CS). WP and WH could be combined with the DCAM approach to reduce energy usage even further (COM).

There have also been some techniques proposed to avoid DTLB accesses. For example, opportunistic virtual caching (OVC) is a technique to allow some blocks in the L1 caches to be cached with virtual addresses by changing the operating system to indicate which pages can use virtual

| -       | companion of D crimi rippi |    |        |          |                               |                              | ~ . |                       |                                        | 0 1100000 | ·   |

|---------|----------------------------|----|--------|----------|-------------------------------|------------------------------|-----|-----------------------|----------------------------------------|-----------|-----|

|         | Data Access Techniques     |    |        |          | Characteristics of Techniques |                              |     |                       |                                        |           |     |

| · · · · | WP Way Prediction          |    |        | MS       | 5                             | m ore $s$ pace required      |     |                       |                                        |           |     |

| '       | WC                         |    | Way    | Cachin   | g                             | OM                           | 1   | overhead on $m$ isses |                                        |           |     |

| י       | WH                         |    | Way    | Haltin   | g                             | CP may be on <i>c</i> ritica |     | ritical $p$ a         | itical $p$ ath                         |           |     |

| ]       | ГLC                        |    | TagLe  | ss Cacl  | he                            | CI                           |     | com                   | piler/IS                               | A change  | es  |

|         | LB                         |    | Line   | Buffer   | •                             | CS CS                        |     | custo:                | m <b>S</b> RA                          | M requir  | red |

|         | $\mathbf{FC}$              |    | Filter | r Cach   | e                             | TD                           | )   | Ta                    | $\mathrm{g}/\boldsymbol{D}\mathrm{TI}$ | B access  |     |

| ן ו     | ГСЕ                        |    | ag Che | eck Elis | sion                          | COI                          | M   | com                   | plemer                                 | nts DCAM  | Л   |

| DA      | AGDA                       | De | couple | d Add    | rGen                          | HC HC                        | ;   | $m{h}$ ię             | gher $c$ o                             | mplexity  |     |

|         |                            |    | & Dat  | a Acce   | ess                           |                              |     |                       |                                        |           |     |

|         |                            |    | MS     | OM       | CP                            | HC                           | C   | [ CS                  | TD                                     | COM       |     |

|         | WF                         | )  |        | Х        |                               |                              |     | X                     | X                                      | X         |     |

|         | WC                         | 2  | Х      |          | Х                             |                              |     | X                     | Х                                      |           |     |

|         | WH                         | I  |        |          |                               | Х                            |     | X                     | X                                      | Х         |     |

|         | TLO                        | C  | Х      |          | Х                             |                              |     |                       |                                        | X         |     |

|         | LB                         |    |        |          | Х                             |                              |     | X                     | X                                      |           |     |

|         | FC                         | ;  | Х      | Х        |                               |                              |     |                       | X                                      |           |     |

|         | TCI                        | Ε  | Х      |          | Х                             | Х                            |     |                       |                                        |           |     |

|         | DAG                        | DA |        |          |                               |                              | X   |                       |                                        |           |     |

Table 3.4: Comparison of DCAM Approach to Various L1 DC Access Techniques

caching [5] (OS). In contrast, the DCAM technique can avoid many DTLB accesses by detecting that the physical page has not changed while requiring no OS changes.

L1 DC tag checks for memory references are eliminated when the cache line to be accessed can be identified by the compiler as being known by using direct address registers (DARs) [29]. The compiler annotates a memory reference that sets a DAR identifying the accessed L1 DC line and subsequent memory references that are guaranteed to access the same line reference the same DAR to avoid the tag check (CI). Unlike the DCAM technique, several compiler transformations are required, such as loop unrolling and alignment of variables on cache line boundaries, to make these guarantees, which can result in both code and data size increases. In addition, the DAR approach requires ISA modifications to support it.

A tagless cache (TLC) design has been proposed that uses an extended TLB (ETLB) to avoid tag checks [24]. While the TLC approach can significantly reduce energy usage, the authors assume the ETLB is accessed first to subsequently allow accessing a single L1 DC data array, which could either increase the cycle time or require an additional cycle to service an L1 DC access (CP). The DCAM approach could be used in conjunction with the TLC approach as the ETLB can be avoided when memoization detects that the L1 DC way is already known (COM). Unlike DCAM, the TLC approach does not avoid TLB accesses (TD). Finally, the use of a TLC requires dealing with synonyms, homonyms, and other problems associated with virtually addressed data accesses.

Other small structures have been suggested to reduce L1 DC energy usage. A line buffer (LB) can be used to hold the last line accessed in the L1 DC [26]. The buffer must however be checked before accessing the L1 DC, placing it on the critical path, which can degrade performance (CP). A line buffer also has a high miss rate, which may increase the L1 DC energy usage due to continuously fetching full lines from the L1 DC memory (OM). A small filter cache (FC) accessed before the L1 DC has been proposed to reduce the power dissipation of data accesses [15]. However, filter caches reduce energy usage at the expense of a significant performance penalty due to their high miss rate (OM), which mitigates some of the energy benefits and has likely discouraged its use.

There are some similarities between the Tag Check Elision (TCE) approach and the DCAM approach [34]. Like DCAM, the TCE approach stores an L1 DC way with each integer register. However, there are several significant differences between TCE and DCAM. The TCE approach is likely to memoize more cases with large displacements. However, this feature comes with several disadvantages as compared to the DCAM approach, as depicted in Table 3.4, including that the TCE complexity may increase the critical path that could affect the cycle time (CP). Unlike TCE, DCAM retains the DTLB way to avoid DTLB accesses when a different line is accessed within the same page. TCE stores a bound with every register to memoize L1 DC ways, which in their evaluation was a 29-bit value (MS). In contrast, DCAM requires no immediate value with DCAS entries, which should require much less power to access. TCE requires two comparisons and an addition to verify that the effective address of the memory reference is within the bounds of the cache line as well as an extra addition and a bound read and write each time an integer register is incremented by a value (CP, HC). DCAM's check for a carry out of an addition into the *set index* field and *VPN* fields is much simpler. Finally, TCE's invalidation scheme requires much more space than DCAM's invalidation method (MS).

The Decoupled Address Generation and Data Access (DAGDA) technique exploits memoization to improve data access energy efficiency. However, all loads and stores are required to utilize zero displacements, requiring both compiler and instruction set architecture (ISA) changes [25].

### 3.8 Conclusions

In this chapter, an approach was described to reduce energy usage by saving L1 DC access information with the register used to access memory. By associating the DTLB access and L1 DC tag check with the base register used in a memory operation the processor is often able to avoid L1 DC tag array accesses and DTLB accesses and access a single L1 DC data array for loads. Furthermore, a technique is shown to retain this information across pointer updates if the updated value falls within the same cache line or page of the source register. These energy saving benefits were able to be obtained on unmodified binaries.

### CHAPTER 4

# AN ENERGY EFFICIENT DESIGN FOR UTILIZING A LEVEL-ZERO DATA CACHE

Level-zero data caches (L0 DCs), also known as data filter caches (DFCs), have been shown to be effective at reducing data access energy usage. However, this energy reduction comes with a performance penalty when the data being accessed is not in the L0 DC as the initial access to the L1 DC is delayed by at least one cycle. In this chapter a design is described for utilizing an L0 DC that both reduces data access energy usage and provides a performance improvement. In contrast to a traditional L0 DC, the L0 DC design proposed in this chapter allows data to be accessed during the level-one data cache (L1 DC) address generation stage. Performance is improved as L0 DC load hits provide the data earlier than the L1 DC, reducing stalls due to load hazards. Data access energy usage is reduced as the proposed L0 DC design is smaller and requires no DTLB access, making it more efficient to access than an L1 DC. This chapter also provides additional techniques that reduce the power for many of the memory operations still accessing the L1 DC.

#### 4.1 Introduction

A level-zero data cache (L0 DC), also known as a data filter cache (DFC), has been shown to be effective at reducing data access energy [14, 15]. An L0 DC is energy efficient since a large fraction of the memory references can be serviced from the L0 DC that is much smaller than a level-one data cache (L1 DC), resulting in less energy usage for each L0 DC reference as compared to an L1 DC reference. However, a conventional L0 DC has disadvantages that has discouraged its adoption in contemporary processors. First, an L0 DC can cause a performance penalty as it has to be accessed before the L1 DC in order to to reduce energy usage. Upon an L0 DC miss, the L1 DC is accessed a cycle later than it normally would, potentially causing load-delay hazards that would not occur had an L0 DC not been used. This increase in execution time will mitigate some of the energy benefit of using an L0 DC. Second, a single cycle L0 line fill as proposed in many prior studies [7, 9, 10, 14, 15, 27] has been shown to be unrealistic as it can adversely affect L1 DC area and energy efficiency [3]. These issues must be resolved for an L0 DC to be a practical alternative for a high performance embedded processor.

This chapter proposes a new design that allows the use of an L0 DC that improves both energy efficiency and performance. The key insight for this design is to dynamically detect instructions that update a register whose value is dereferenced by a load or a store and to keep these register values in a small structure that can be accessed a cycle earlier in the pipeline. This feature allows the effective address to be calculated a cycle earlier so that the L0 DC can be accessed a pipeline stage before the L1 DC is conventionally accessed.

Our design for utilizing an L0 DC makes the following contributions. (1) In contrast to a conventional L0 DC that degrades performance, accessing the L0 DC data early provides a small performance improvement by avoiding many load hazard stalls and removing the potential performance penalty typically associated with L0 DCs. (2) Data access energy usage is reduced not only because the L0 DC is smaller than an L1 DC, but also because the proposed L0 DC design does not require a DTLB access. (3) L1 DC access information obtained during the L0 DC access allows the L1 DC to be more efficiently accessed when servicing L0 DC misses, writing through to the L1 DC, and filling words within an L0 DC line from the L1 DC.

### 4.2 Proposed L0 DC Design

In this section an approach is described for utilizing an L0 DC to both improve performance and reduce energy usage. This section provides a high-level overview of the design.

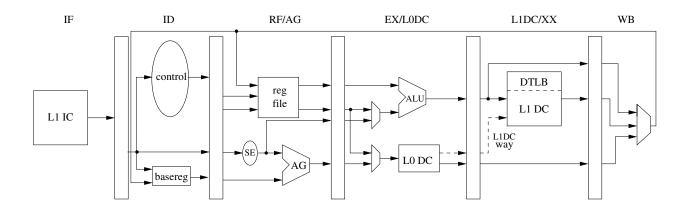

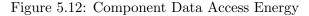

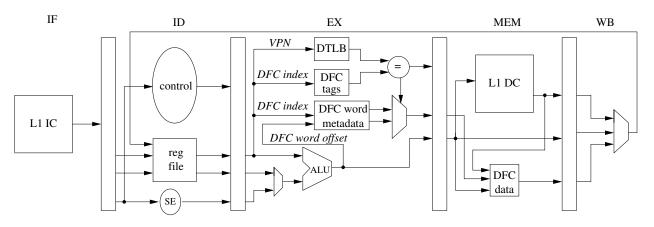

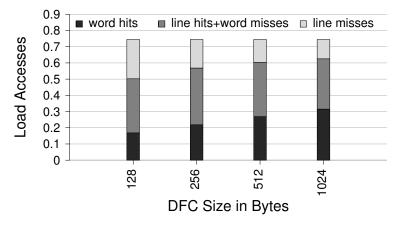

Figure 4.1 shows a high-level datapath for ALU and load instructions in a six stage instruction pipeline that is utilized in this chapter. Loads from the L0 DC occur during the fourth (L0DC) stage and loads from the L1 DC occur during the fifth (L1DC) stage. Loads from the L0 DC are possible one cycle before the L1 DC is accessed when the effective address (base register plus displacement) can be calculated during the RF stage. To accomplish this, the base register of the load is obtained during the ID stage from the *basereg* structure, a small subset of the register file used by loads and stores. Since the displacement value is available immediately from the instruction bits, the effective address can be computed during the RF stage. Alternatively, if the displacement of the load is zero, there is no need to calculate the effective address. In this case, the effective address is simply the base register value which can be obtained from the register file. Using this

Figure 4.1: Datapath for ALU and Load Instructions

early effective address computation strategy, the data can be obtained from the L0 DC during the address generation (AG) stage, one cycle before the the L1 DC is accessed during the MEM stage.

Having the L0 DC and L1 DC always accessed in a given pipeline stage helps to avoid structural hazards and simplifies the pipeline. Each L0 DC line contains the corresponding L1 DC way in which it resides, which is used to make L1 DC accesses more efficient when they are needed to be performed. The DTLB is only accessed when accessing the L1 DC and the L1 DC way is unknown. Forwarding paths and the internal pipelining for the L0 DC and L1 DC to handle stores are not shown to simplify the figure.

The L0 DC in this design will not be accessed on every load instruction since sometimes the base register value is not available from the *basereg* structure and the displacement is not zero. One strategy would be to access the L0 DC after the effective address is calculated during the AG stage. However, an L0 DC miss could cause a performance penalty as the data would be retrieved from higher levels of cache a cycle later than it normally would. Instead, it would be desirable to load the data from the L1 DC instead of waiting until the address generation is complete to access the L0 DC, effectively removing the performance penalty typically associated with L0 DCs. Since the data can be retrieved from either the L0 DC or the L1 DC the processor needs to ensure that data in the L1 DC has the same values as any data that are resident in the L0 DC. An inclusive cache policy and an L0 DC write-through policy are used to ensure that the L1 DC always has the most recent data. A write-through policy is much simpler to implement than a write-back policy as the processor does not have to deal with writing back dirty L0 DC lines over multiple cycles, which

would allocate the L0 DC read port, making the L0 DC inaccessible during this period. Instead, evicted L0 DC lines simply need to be invalidated.

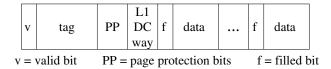

Figure 4.2 shows the information that will be contained in each L0 DC line. The page protection bits are copied from the DTLB when the L0 DC line is allocated. This is necessary to ensure that data is accessed properly as the DTLB is avoided during L0 DC hits, as described is Section 4.3.5. An L0 DC line also identifies the L1 DC way where the L0 DC line resides. Each data byte within the line has a filled bit to indicate if that byte within the line is resident, described in Section 4.3.4.

Figure 4.2: L0 DC Line Contents

The remainder of this section is used to describe the design in more detail.

#### 4.3 Utilizing an L0 DC to Improve Performance

The following subsections describe how this design makes base register values available earlier in the pipeline, is integrated into a pipeline, fills data words in an L0 DC line, and is virtually addressed.

#### 4.3.1 Making Base Register Values Available Earlier in the Pipeline

A simple approach to ensure that base register values are available in the *basereg* structure is to have all integer instructions that update a register to write their register value to the *basereg* structure. There are two problems with this approach: 1) the energy-saving benefits of using an L0 DC are mitigated due to unnecessary *basereg* writes and 2) additional pressure is placed on the basereg structure, meaning it will be harder to retain *basereg* values long enough so that they can be used by loads and stores because they will be evicted by unnecessary *basereg* writes.

To solve these problems, an approach is described to dynamically detect instructions that update an integer register whose value will be dereferenced by a load or a store. Such registers are referred to as base registers since they contains the base value of the effective address for a load or a store. Such instructions are referred to as base address generation (BAG) instructions as they update the base register of a load or store. Table 4.1 shows the different MIPS instructions that are likely to be a BAG instruction and account for over 99.9% of the BAG instructions. An instruction with one of these opcodes is referred to as a potential BAG (PBAG) instruction.

|           |              |                      | -                    |                                 |

|-----------|--------------|----------------------|----------------------|---------------------------------|

| Size      | Type         | Operation            | MIPS Inst Effect     | Source Operands                 |

|           | Local        | (1) int immed add    | rd = rs + immed      | stack pointer and offset        |

| Scalar    | Global       | (2) bitwise immed OR | $rd = rs \mid immed$ | high   low global address       |

|           | Pointer      | (3) int load         | rt = M[rs]           | pointer variable address        |

|           | Array Elem   | (4) int reg add      | rd = rs + rt         | array address + elem offset     |

| Composite | Struct Field | (1) int immed add    | rd = rs + immed      | struct address $+$ field offset |

|           | Ptr Arith    | (5) int reg sub      | rd = rs - rt         | pointer - var offset            |

Table 4.1: Last Instruction to Compute a Data Address

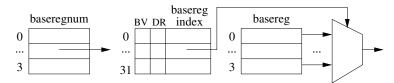

When a PBAG instruction is executed, a small basered structure as depicted in Figure 4.3 is updated. Each basered element contains the value of an integer register that was dereferenced in a load or store instruction. The structure shown in the figure contains at most four base register values. The basered structure is indexed by the base register number of a load or store instruction and is used to select the base register value from a multiplexor. The BV (Base register Valid) bit indicates if the integer architectural register currently points to a basered element. The DR (DeReferenced) bit indicates if the base register has been dereferenced by a load or a store with a nonzero displacement. The processor will update the basered element during the WB stage of a BAG instruction. A separate basered number structure contains for each basered element the integer register number associated with that value. The LRU element of the basered structure is replaced if there is not a valid value already associated with the base register number and the basered is used to clear the BV bit of the replaced basered element.

Figure 4.3: Base Register Structure

#### 4.3.2 Using Base Register Values in Loads and Stores

Similar to how to the number of unnecessary *basereg* writes have been reduced, a technique is proposed to reduce the number of unnecessary *basereg* reads. Ideally, a *basereg* element is

accessed only during load and store instructions that use a non-zero displacement value so there are no unnecessary basereg reads, which mitigate the energy savings of the approach. However, since the instruction type isn't known until the end of the ID stage and possibly the register number depending on the instruction set architecture, this section describes an approach which approximates this behavior.

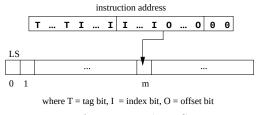

A bit is associated with each instruction in the L1 IC, called the LS (Load/Store) bit, to classify instructions that are a load or store with a nonzero displacement (when any bits in the immediate field are not zero) as shown in Table 4.2. The reason the processor checks for a nonzero displacement is that a load or store with a zero displacement does not need to access the *basereq* structure as described in Section 4.3.3. This LS bit associated with an instruction is read each time during the instruction fetch (IF) pipeline stage.

Table 4.2: Value Associated with the LS Bit

|   | Meaning                                   |

|---|-------------------------------------------|

| 0 | otherwise                                 |

| 1 | load or store with a nonzero displacement |

Instructions with a PBAG opcode as shown in Table 4.1 comprise a significant fraction of the instructions executed. It is desirable to only update the *basereq* when an actual address is being generated as unnecessary *basereq* updates expend additional energy and may replace useful *basereq* values. The following technique is used to avoid unnecessary updates to the basereg structure. The DR (dereferenced) bit in Figure 4.3 is set when a register is dereferenced by a load or a store with a nonzero displacement where the PBAG instruction was executed in time for the *basereq* structure to be dereferenced. When a BAG instruction sets a register that has its DR bit set, then the BAG instruction will update the *basereg* structure and set the BV bit in Figure 4.3. This approach works well as a register that is used to access memory in loops is often not set by other non-PBAG instructions. Note that non-PBAG instructions will clear both the BV and DR bits associated with the register number being updated.

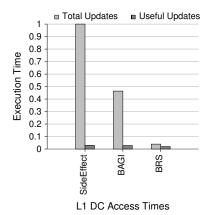

Figure 4.4 shows a comparison of several different approaches that can be used to determine which instructions will update the *basereq* structure. One approach that can be used is to allow all instructions that update to an integer register to write their result to the *basereg* structure, referred to as the "Side Effect" approach as all instructions with an integer side effect write to it. However,

Figure 4.4: Comparison of BRS Update Approaches

as shown in the figure, only about 2.8% of these instructions will have their *basereg* element used by a load or store instruction. This is because many instructions 1) don't update a register used by a load or store instruction, 2) update a register that is used by a load or a store whose displacement value is zero and thus doesn't need to access the *basereg* structure, or 3) updates a register that is used by a load or a store but whose value will not be ready in time to be read from the *basereg* structure. An additional approach used is to only update *basereg* structure for BAG instructions (BAGI), which constitute the vast majority of instructions that are the last to update a register before the register is used in a load or store. This filters out approximately 61% of unnecessary basereg writes. However, this still updates the *basereg* structure 15 times unnecessarily for every one update eventually used by a load or store. Utilizing the DR bit to detect registers that are used by loads and stores only updates the *basereg* structure for about 4% of all instructions, of which, about half of them are used by subsequent loads and stores. This approach drastically reduces the number of updates to the *basereg* structure, enabling the *basereg* structure to use fewer elements as there is less pressure due to unnecessary updates evicting useful entries.

#### 4.3.3 Integrating L0 DC Accesses into the Instruction Pipeline

Table 4.3 describes the different integer instruction pipeline stages used in this study. Note many of the names for these stages occur at the same time in the pipeline, but distinct names are provided to facilitate understanding what pipeline actions are performed by different instructions. This pipeline separates the ID (instruction decode) and RF (register fetch) stages to reduce energy usage caused by unnecessary register fetches. The *basereg* structure is accessed during the ID stage of an instruction marked as a load or store with a nonzero displacement (see Table 4.2) to obtain the base register value. The AG (address generation) stage performs an addition with this base register value and the displacement to calculate the effective memory address.

|       |                    |       | 1 0                          |

|-------|--------------------|-------|------------------------------|

| Stage | Meaning            | Stage | Meaning                      |

| IF    | instruction fetch  | LOTC  | L0 DC tag check              |

| ID    | instruction decode | L1TC  | L1 DC tag check              |

| RF    | register fetch     | WB    | write back                   |

| AG    | address generation | TC    | L0 DC/L1 DC tag check        |

| EX    | execute            | DCW   | L0/L1 DC write, no tag check |

| LODC  | L0 DC access       | L1W   | L1 DC write, no tag check    |

| L1DC  | L1 DC access       | XX    | stage not used               |

Table 4.3: Instruction Pipeline Stages

Table 4.4 shows how different instructions proceed through a six stage pipeline utilizing the pipeline stages shown in Table 4.3. Note this design can easily be adapted to work with additional pipeline stages supporting a multicycle L1 DC load access.

| Table 1.1. Stages eset by Instituctions |                 |    |    |      |      |     |  |

|-----------------------------------------|-----------------|----|----|------|------|-----|--|

| Instruction                             | Pipeline Stages |    |    |      |      |     |  |

| Instruction                             | 1               | 2  | 3  | 4    | 5    | 6   |  |

| (a)ALU inst                             | IF              | ID | RF | EX   | XX   | WB  |  |

| (b)L1 load hit                          | IF              | ID | RF | EX   | L1DC | WB  |  |

| (c) L0 load hit                         | IF              | ID | AG | LODC | XX   | WB  |  |

| (d)L0 load hit no disp                  | IF              | ID | RF | LODC | XX   | WB  |  |

| (e) L0 load miss                        | IF              | ID | AG | LODC | L1DC | WB  |  |

| (f) L0 load miss no disp                | IF              | ID | RF | LODC | L1DC | WB  |  |

| (g)L1 store hit                         | IF              | ID | RF | EX   | TC   | DCW |  |

| (h)L0 store hit                         | IF              | ID | AG | LOTC | XX   | DCW |  |

| (i) L0 store hit no disp                | IF              | ID | RF | LOTC | XX   | DCW |  |

| (j) L0 store miss                       | IF              | ID | AG | LOTC | L1TC | L1W |  |

| (k)L0 store miss no disp                | IF              | ID | RF | LOTC | L1TC | L1W |  |

Table 4.4: Stages Used by Instructions

An *ALU inst* (case (a) in Table 4.4) proceeds through the pipeline and does not perform any action (XX) in the 5th pipeline stage. A BAG ALU instruction also writes to the *basereg* structure in the sixth stage.

An L1 load hit or L1 store hit (cases (b) and (g) in Table 4.4) operation means that the base register value was not available in the *basereg* structure and the load or store will access the L1 DC. An L1 store hit will require that both the L0 DC and the L1 DC to be updated when the data line is resident in the L0 DC since the L0 DC uses an inclusive cache policy. The L0 DC tag arrays are replicated to allow an L0 DC tag check in either the L0DC or L1DC stages without causing a structural hazard.

All operations beginning with L0 means the L0 DC is accessed. For cases (c) and (d) in Table 4.4, the load hits in the L0 DC and no L1 DC access is performed. In the cases of (d), (f), (i), and (k) in Table 4.4, the displacement of the load and store is zero, meaning no address calculation is necessary and the processor does not access the *basereg* structure. For cases (c), (e), (h), and (j) in Table 4.4, the load/store has a non-zero displacement and the processor obtains the base register value from the *basereg* structure in the ID stage in order to complete the address calculation in the AG stage, where a separate adder is utilized to avoid a structural hazard. Note an AG stage does not access the register file when the base register value had already been obtained during the ID stage from the *basereg* structure. For cases (e), (f), (j), and (k) in Table 4.4, the L0 DC is accessed but the word being accessed is not resident and the processor accesses the L1 DC in the following cycle.

The basereg structure is only accessed when an instruction has been marked in the LS bit vector as a load or store instruction with a nonzero displacement. The base register value is not available in the basereg structure when the base register value for a particular register in the basereg structure was replaced or the base register value was not calculated in time to perform an address calculation in the AG stage. The base register value can be forwarded to the AG stage of a load or store after the EX stage of a BAG ALU instruction, the L0DC stage of BAG load that hits in the L0 DC, or the L1 DC stage of a BAG load that obtains its value from the L1 DC. However, there must be at least one instruction between the ALU BAG instruction (or a BAG load that hits in the L0 DC) and the load or store that uses the BAG instruction destination register so that the value can either be read from the basereg structure or forwarded to the AG stage of the load or store instruction. A BAG load that obtains its value from the L1 DC must be separated from the load or store that uses the value from the L1 DC must be separated from the load or store that uses the value from the L1 DC must be separated from the load or store that uses the value from the L1 DC must be separated from the load or store that uses the value by at least two instructions for forwarding to occur. Note that if forwarding cannot occur, then the L1 DC is accessed to avoid pipeline delays.

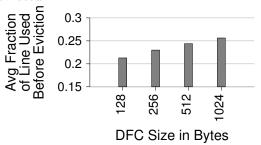

### 4.3.4 Filling L0 DC Lines

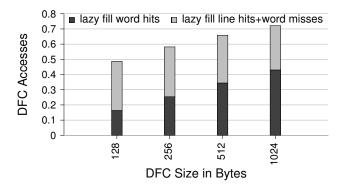

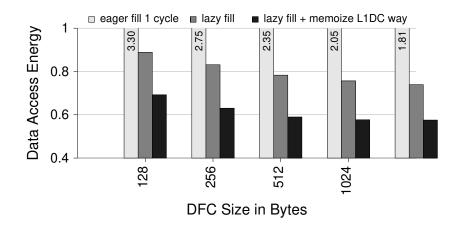

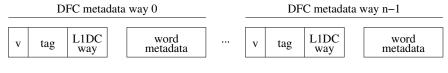

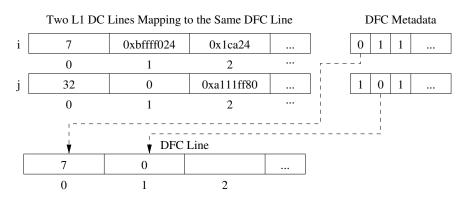

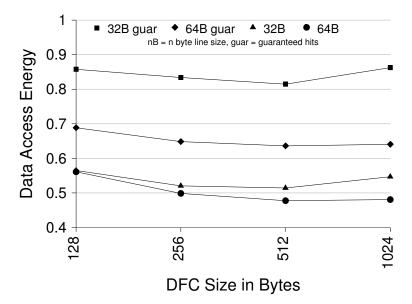

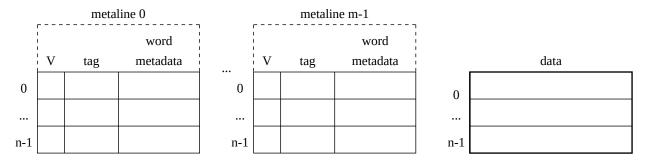

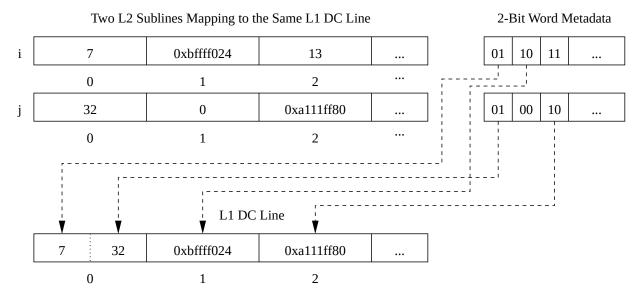

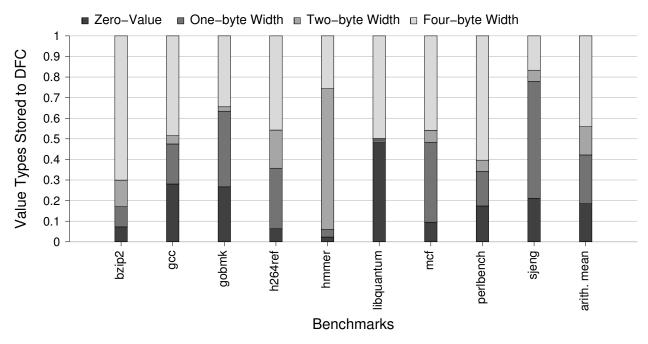

While the L0 DC line size can be smaller than an L1 DC line, it is still advantageous to utilize a multiword L0 DC line size to exploit spatial locality in data references. Many prior filter cache studies have assumed that an L0 line is the same size as an L1 line and can be filled in a single cycle to reduce the L0 miss penalty [7,9,10,14,15,27]. Such an assumption is unrealistic as reading an entire line from an L1 DC in a single cycle requires a larger bitwidth, which could increase the area of the L1 DC and negatively affect both L1 DC access time and access energy. In addition, some applications referenced only a single word from an L0 DC line before the L0 DC line was evicted.