## THE FLORIDA STATE UNIVERSITY

#### COLLEGE OF ARTS & SCIENCES

# REDUCING THE COST OF COMPARISONS WITHIN CONDITIONAL TRANSFERS OF CONTROL

By

# WILLIAM C. KREAHLING

A Dissertation submitted to the Department of Computer Science in partial fulfillment of the requirements for the degree of Doctor of Philosophy

> Degree Awarded: Summer Semester, 2005

The members of the Committee approve the dissertation of William C. Kreahling defended on July 12, 2005.

David Whalley Professor Directing Dissertation

Steve Bellenot Outside Committee Member

Robert van Engelen Committee Member

Ashok Srinivasan Committee Member

Xin Yuan Committee Member

The Office of Graduate Studies has verified and approved the above named committee members.

This work is dedicated to Dr. Alice McRae, the one who started me down this road in the first place. And to my family, who supported me through the good times and the bad. It's those bad ones that count.

# ACKNOWLEDGMENTS

I would like to thank Steve Hines, Prasad Kulkarni and Clint Whaley, for all your support, technical and moral. I think you guys understand the heart attack! I would also like to thank my advisor, Dr. David Whalley. This work could not have been done without his help.

# TABLE OF CONTENTS

| $\operatorname{Lis}$ | st of Tables $\ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | viii                                                                                                                                                                                    |

|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $\operatorname{Lis}$ | st of Figures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ix                                                                                                                                                                                      |

| Ab                   | ostract                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | xii                                                                                                                                                                                     |

| 1.                   | INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1                                                                                                                                                                                       |

|                      | <ol> <li>Separate Compare and Branch Instructions</li> <li>Single Compare and Branch Instruction</li> <li>New Techniques Focusing on the Comparison</li> </ol>                                                                                                                                                                                                                                                                                                                                                                | $\begin{array}{c} 1 \\ 2 \\ 3 \end{array}$                                                                                                                                              |

|                      | 1.4 Organization of Dissertation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 3                                                                                                                                                                                       |

| 2.                   | RELATED WORK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 4                                                                                                                                                                                       |

|                      | <ul> <li>2.1 Delayed Branches.</li> <li>2.2 Branch Prediction</li> <li>2.2.1 Branch Prediction Buffer</li> <li>2.2.2 Correlating Predictors</li> <li>2.2.3 Tournament Predictors</li> <li>2.2.4 Markov Predictors</li> <li>2.2.5 Neural Methods for Branch Prediction</li> <li>2.3 Branch Target Buffer</li> <li>2.4 Branch Registers</li> <li>2.5 Predication</li> </ul>                                                                                                                                                     | $ \begin{array}{c} 4 \\ 5 \\ 6 \\ 7 \\ 7 \\ 8 \\ 9 \\ 9 \end{array} $                                                                                                                   |

|                      | <ul> <li>2.6 Loop Transformations</li> <li>2.6.1 Loop Unrolling</li> <li>2.6.2 Loop Unswitching</li> <li>2.7 Avoiding Conditional Branches</li> <li>2.7.1 Intraprocedural Conditional Branch Elimination</li> <li>2.7.2 Interprocedural Conditional Branch Elimination</li> <li>2.8 Transforming Conditional Branches into Indirect Jumps</li> <li>2.9 Compiler Support for Predicated Execution</li> <li>2.9.1 The Hyperblock</li> <li>2.10 Control CPR for EPIC Architectures</li> <li>2.11 TERA Computer System</li> </ul> | $     \begin{array}{c}       3 \\       10 \\       10 \\       10 \\       11 \\       11 \\       11 \\       12 \\       13 \\       13 \\       14 \\       15 \\     \end{array} $ |

| 3. | CONDITION MERGING                                                                                                                                                                                                                                                                                                                                                     | 16             |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

|    | <ul> <li>3.1 Introduction</li> <li>3.2 Merging Conditions that Involve a Single Variable</li> <li>3.2.1 Eliminating Logically Redundant Branches</li> <li>3.2.2 Merging Not Equal Tests Using Range Checks</li> <li>3.2.3 Merging Bit Tests</li> <li>3.4 Merging into a Sufficient Condition</li> <li>3.5 Applying the Transformation</li> <li>3.6 Results</li> </ul> | 18             |

| 4. | REDUCING COSTS BY DECOUPLING THE SPECIFICATION<br>OF THE COMPARISON                                                                                                                                                                                                                                                                                                   | 44             |

|    | <ul> <li>4.1 Implicit Comparisons</li></ul>                                                                                                                                                                                                                                                                                                                           | 70             |

| 5. | FUTURE WORK                                                                                                                                                                                                                                                                                                                                                           | 86             |

|    | <ul> <li>5.1 Condition Merging</li></ul>                                                                                                                                                                                                                                                                                                                              | 86<br>87<br>88 |

| 6.  | CONCLUSIONS       | 90 |

|-----|-------------------|----|

| RE  | FERENCES          | 93 |

| BIC | OGRAPHICAL SKETCH | 96 |

# LIST OF TABLES

| 3.1 | SPARC Code Generation Strategies for Merged Bit Tests                                        | 22 |

|-----|----------------------------------------------------------------------------------------------|----|

| 3.2 | Rules for Merging Conditions Comparing Multiple Variables into a Single Equivalent Condition | 26 |

| 3.3 | Rules for Merging Conditions Comparing Multiple Variables into a Single Sufficient Condition | 28 |

| 3.4 | Test Programs                                                                                | 37 |

| 3.5 | Dynamic Results from Applying the Individual Techniques                                      | 38 |

| 3.6 | The Number of Conditions Merged                                                              | 43 |

| 4.1 | Test Definitions and their Complements                                                       | 54 |

| 4.2 | Benchmarks Tested                                                                            | 62 |

| 4.3 | Reasons Comparisons Could not be Made Implicit                                               | 63 |

| 4.4 | Operational Latencies                                                                        | 65 |

| 4.5 | New Instructions for Comparison Specifications                                               | 78 |

| 4.6 | Encoding for the New ARM Instructions                                                        | 78 |

| 4.7 | Benefits Using Alternate Branch Prediction Method                                            | 83 |

|     |                                                                                              |    |

# LIST OF FIGURES

| 3.1  | Merging Three Conditions                                                                                  | 17 |

|------|-----------------------------------------------------------------------------------------------------------|----|

| 3.2  | Compilation Process for Merging Conditions                                                                | 18 |

| 3.3  | Merging Logically Redundant Conditions                                                                    | 19 |

| 3.4  | Merging Other Logically Redundant Conditions                                                              | 19 |

| 3.5  | Merging Not Equal Tests Using Range Checks                                                                | 21 |

| 3.6  | Merging Bit Tests                                                                                         | 21 |

| 3.7  | Other Benefits from Reducing Scalars to Single Bits                                                       | 24 |

| 3.8  | Merging Conditions That Test If Different Variables Are Equal to Zero                                     | 25 |

| 3.9  | Code Generated for the Merged Condition That Checks If <i>n</i> Variables Are Equal to Zero               | 25 |

| 3.10 | Increasing Merging Opportunities by Unrolling Loops                                                       | 27 |

| 3.11 | Merging Conditions That Check If Different Variables Are Not Equal to Zero                                | 28 |

| 3.12 | Rule 7 is Implied by Rule 8                                                                               | 29 |

| 3.13 | Using Rule 8 Efficiently with a Single Variable                                                           | 30 |

| 3.14 | Merging Conditions That Check If Multiple Variables Are Not Equal to Loop-Invariant Values                | 31 |

| 3.15 | Merging Conditions That Check If Multiple Unsigned Variables Are<br>Less Than an Unsigned Invariant Value | 32 |

| 3.16 | Paths That Do Not Cross Loop Boundaries                                                                   | 32 |

| 3.17 | A Set of Conditions to be Merged May be Connected by Multiple<br>Subpaths                                 | 34 |

| 3.18 | Overview of Condition Merging Optimization                                                                | 35 |

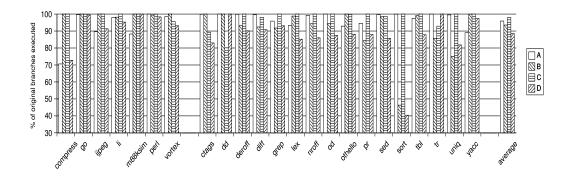

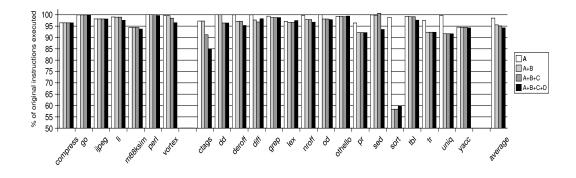

| 3.19 | Effect on Branches Executed for Each Technique                                                            | 39 |

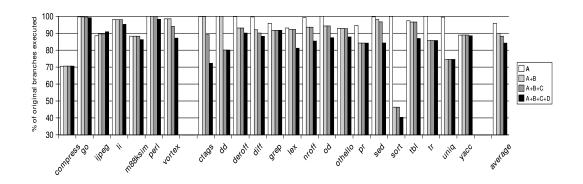

| 3.20 | Cumulative Effect on Branches Executed                                                                    | 40 |

| 3.21 | Cumulative Effect on Instructions Executed                                                                | 40 |

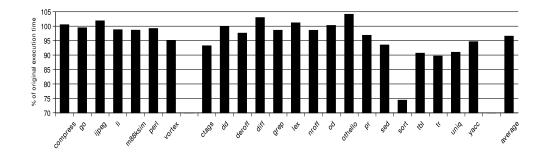

| 3.22 | Effect on Execution Time                                                                                  | 41 |

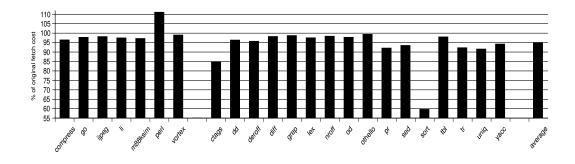

| 3.23 | Effect on Estimated Fetch Cost for a 16KB Two-Way Associative Instruction Cache | 4  |

|------|---------------------------------------------------------------------------------|----|

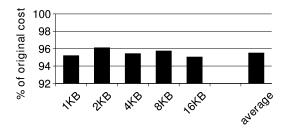

| 3.24 | Average Fetch Cost for a Variety of Cache Sizes                                 | 4  |

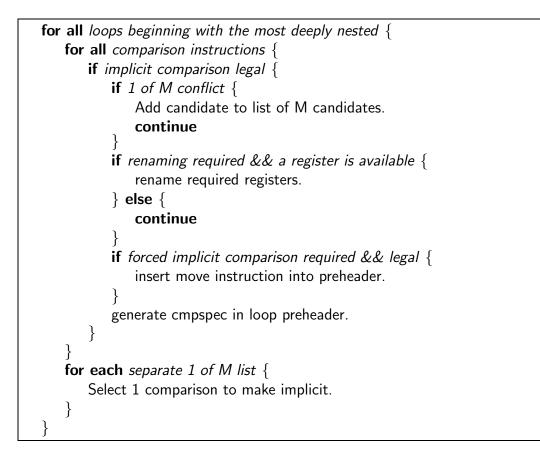

| 4.1  | High Level Algorithm for Implicit Comparisons                                   | 4  |

| 4.2  | C Code                                                                          | 5  |

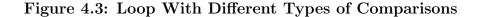

| 4.3  | Loop With Different Types of Comparisons                                        | 5  |

| 4.4  | Post-Domination Requirement                                                     | 5  |

| 4.5  | After Loop Invariant Code Motion                                                | Ę  |

| 4.6  | Applying CSE to Implicit Comparisons                                            | Ę  |

| 4.7  | Comparison Specification with Branch Register Negation                          | Ŀ  |

| 4.8  | Register Renaming in a Single Live Range                                        | 5  |

| 4.9  | Both Comparison Specifications Moved Outside the Loop                           | ļ  |

| 4.10 | Making 1 of M Candidates Invariant                                              | L, |

| 4.11 | Adding a Forced Move to a Loop                                                  | 5  |

| 4.12 | Comparison Specification Encoding                                               | L, |

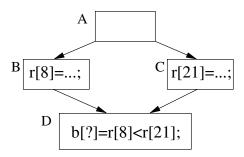

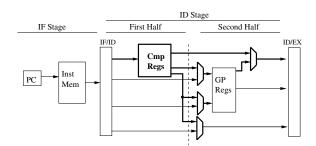

| 4.13 | Five-Stage Pipeline with Additional Hardware                                    | (  |

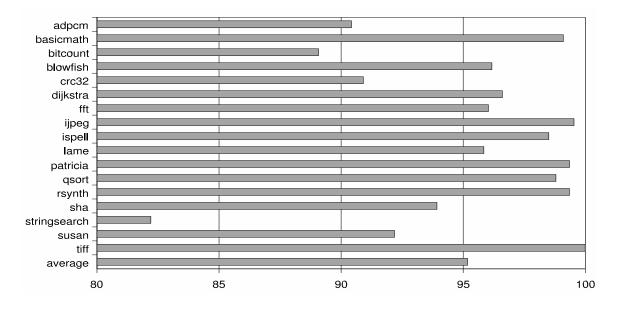

| 4.14 | Percentage of Instructions Executed                                             | 6  |

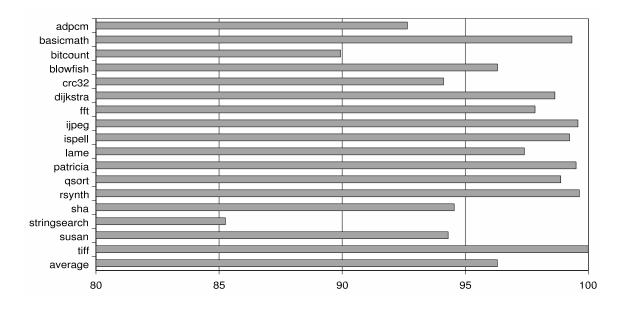

| 4.15 | Percentage of Execution Cycles                                                  | (  |

| 4.16 | Overview of Modified Decode Stage                                               | (  |

| 4.17 | Comparison Specification and Cbranch RTLs                                       | (  |

| 4.18 | Pipeline Diagram for Load, Traditional Comparison and Branch                    | (  |

| 4.19 | Pipeline Diagram for Load, Cmpspec and Cbranch                                  | 7  |

| 4.20 | Moving Cmpspecs Out of Loops                                                    | 7  |

| 4.21 | Pipeline Diagram for Loop Invariant Comparison Specification                    | 7  |

| 4.22 | Renaming Comparison Specifications                                              | 7  |

| 4.23 | Eliminating Redundant Comparison Specifications                                 | 7  |

| 4.24 | Reversing Branch Condition and Performing CSE                                   | 7  |

| 4.25 | Making Two Compares Use the Same Constant                                       | 7  |

| 4.26 | CSE with a Register and Constant                                                | 7  |

| 4.27 | Instruction Encoding                                                            | •  |

| 4.28 | Different Representations of a Cmpspec RTL                                      | •  |

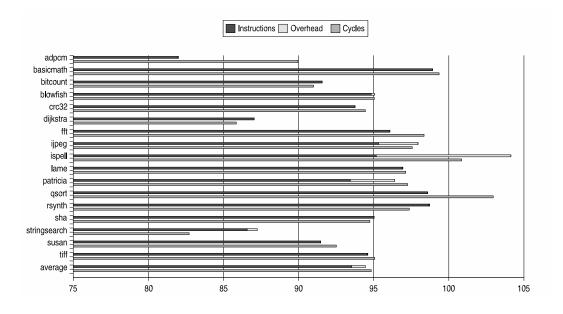

| 4.29 | Percentage of Instructions and Cycles Executed                                  | 8  |

| 4.30 | Percentage of Micro-ops Saved Using Different Prediction Methods | 82 |

|------|------------------------------------------------------------------|----|

| 4.31 | Percentage of Cycles Saved Using Different Prediction Methods    | 83 |

| 5.1  | CSE by Renaming Registers                                        | 89 |

# ABSTRACT

A significant percentage of execution cycles are devoted to performing conditional transfers of control, which occur frequently, cause pipeline flushes when mis-predicted and can prevent other code improving transformations from being applied. The work required for each conditional transfer of control can be broken into three portions: the comparison, the calculation of the branch target address and the actual transfer of control. Most of the research investigating the reduction of costs associated with these instructions have focused on the calculation of the branch target address or the actual transfer of control, overlooking the comparison portion.

In this dissertation we propose several techniques to reduce the costs associated with the comparison portion of conditional transfers of control. The first technique attempts to merge multiple conditions, avoiding the execution of comparison and branch instructions. The other two methods decouple the definition of the values to be compared with the actual comparison itself. In the second technique the comparison becomes an effect that implicitly occurs whenever specified registers are assigned values, avoiding the execution of a separate comparison instruction. The third technique uses a similar concept, but instead of implicit comparisons, it uses a single comparison and branch instruction in conjunction with a comparison specification. This technique attempts to capture the advantages of common branching techniques used today, without the traditional disadvantages of using a single instruction to perform both the comparison and branch.

## CHAPTER 1

# INTRODUCTION

The goal of this research is to reduce the costs associated with conditional transfers of control. Conditional transfers of control can be typically broken into three separate portions. First, a comparison or boolean test between two values is performed. The result of the comparison is typically stored in another register (condition code, general purpose, or predicate) and will later be accessed by a branch instruction. Second is the calculation of the branch target address. The branch target address is typically encoded within the branch instruction, often as a displacement. If the result of the comparison indicates the branch is *taken*, then the address of the next instruction to be fetched must be calculated. Third, the branch instruction itself indicates where the actual transfer of control takes place. The branch instruction accesses the result of the comparison instruction and the next instruction is fetched. The next instruction is either the next sequential instruction or the instruction located at the branch target address. There has been much research conducted with the goal of reducing the costs associated with performing conditional transfers of control. However, the majority of this research has focused on reducing the cost of the calculation of the branch target address and/or the actual transfer of control, while the comparison portion has been largely overlooked.

# **1.1** Separate Compare and Branch Instructions

Arguably the most common method used to perform conditional transfers of control uses separate comparison and branch instructions. One advantage with this method is freedom to encode the comparison and branch instructions, since two separate instructions are used. When the branch instruction is reached, the execution of the program does not stall waiting for the outcome of the comparison to be known before fetching the next instruction to execute on most processors. Instead, a prediction is made and an instruction is fetched. If the prediction was found to be incorrect when the outcome of the comparison is known, then the pipeline is flushed and instructions from the correct path are fetched. Most branch prediction methods used today are accurate enough that this mis-prediction penalty is infrequently assessed. A disadvantage with this method is there are two separate instructions that need to be fetched and decoded to perform the conditional transfer of control. Although execution does not stall when the branch is reached because of branch prediction, execution on an in-order pipeline will stall when the comparison instruction is reached and the values involved in the comparison are not ready, meaning that the branch instruction following the comparison is stalled as well.

#### **1.2** Single Compare and Branch Instruction

Another way of performing conditional transfers of control is to use a single instruction that performs both the comparison and the branch. Using this method the information needed for the comparison is encoded within the branch instruction itself. Thus, only a single instruction is fetched and decoded for each conditional transfer of control. However, to encode all this information within the bits allocated for a single instruction, fewer bits are typically designated to specify the branch target address. This limits the range of branch target displacements. Likewise comparisons to an arbitrary constant sometimes cannot be made.

#### **1.3** New Techniques Focusing on the Comparison

This dissertation presents three different techniques that reduce the costs associated with conditional transfers of control. Unlike the majority of research in this area, these three techniques focus on the comparison portion of a conditional transfer of control. The first technique tries to reduce the number of comparisons needed in a program by testing multiple conditions at once. A condition is a test whose outcome evaluates to *true* or *false*. The second technique decouples the definition of the values to be compared with the actual comparison itself. The comparison becomes an implicit effect that occurs when values are assigned to specified registers. The third technique also decouples the definition of the values involved in the comparison from the actual comparison, using a single comparison and branch instruction in conjunction with an instruction that defines the comparison that will take place. This technique minimizes the disadvantages associated with other techniques that use a single instruction to perform both a comparison and a branch.

#### 1.4 Organization of Dissertation

The remainder of this dissertation is organized in the following manner: Chapter 2 presents an overview of previous work to reduce costs associated with conditional transfers of control. Chapter 3 presents our technique that reduces the cost of traditional transfers of control by testing multiple conditions at once. Chapter 4 discusses the other two techniques, both of which involve a new instruction called a *comparison specification*. In this section we contrast the two techniques and evaluate experimental results from both. Chapter 5 discusses ways that all three techniques might be improved. Finally, Chapter 6 summarizes our findings and presents our research contributions.

#### CHAPTER 2

# **RELATED WORK**

Research into eliminating conditional transfers of control or reducing the costs associated with conditional transfers of control is an ongoing area of research. This section looks at several techniques that have been developed in the past that have been used to combat the problem of delays associated with branch instructions.

#### 2.1 Delayed Branches

A very simple and straightforward technique to reduce the cost of stalls from *taken* or *not-taken* branches is *delayed branches*. In an architecture that supports delayed branches, one or more instructions immediately following the branch instruction are always executed regardless of whether or not the branch is taken. The slots immediately following the branch instruction are called *delay slots*.

A critical component to the success of delayed branches is the ability of the compiler to fill the delay slots with instructions that can safely be executed regardless of the outcome of the branch. If no instruction can be found that will safely execute in a delay slot, then the compiler will fill the slot with a *no-op* instruction. Moving an instruction from the code *before* the branch is always a useful way to fill a delay slot, as code that occurs before the branch needs to be executed no matter the outcome of the branch. However, moving instructions from either the *taken* or *not-taken* paths following the branch may or may not perform useful work. To move an instruction from either the *taken* or *not-taken* paths the instruction must be safe to move to a delay slot. For example, if an instruction is moved from the *taken* flow of control,

it must be safe and legal for that instruction to execute if the branch resolves to *not-taken*, and vice-versa. Measurements have shown that a C optimizing compiler is able to fill between 40% and 60% of delay slots following conditional transfers of control and 90% following unconditional transfers of control [1]. The more delay slots following a branch instruction, the harder it is for the compiler to fill all the slots with instructions that perform useful work.

In some architectures the instructions in the delay slots are able to be conditionally nullified depending on the outcome of the branch. This enables the compiler to choose more instructions to fill the delay slots. An instruction moved from the *taken* path and used to fill a delay slot, no longer has to be safe or legal to execute if the branch is *not-taken*. An instruction in the delay slot will execute if the branch condition resolves a certain way and will be nullified if the branch resolves in the opposite manner. As multiple issue machines rise in popularity, delayed branches are falling out of favor, in part due to the difficulty of filling the delay slots with useful instructions.

#### 2.2 Branch Prediction

The instruction that sequentially follows a branch may not be the next instruction to be executed. If a branch is taken, then the next instruction to be executed is at the address denoted by the branch target address. The flow of control of a program forks at a conditional branch instruction and a decision must be made about which instruction to execute next. In a pipelined machine, if we do not fetch an instruction until we know what instruction executes next, then the CPU will sit idle wasting time and resources. The process of deciding which instruction to execute before we know the outcome of the branch is called *branch prediction*.

#### 2.2.1 Branch Prediction Buffer

Hardware prediction successfully reduces branch costs when it accurately predicts the direction a branch will take [2]. In a *branch prediction buffer* (BPB) the low order bits of an instruction are used to index into a table. Prediction bits are used from this table to predict the outcome of a branch. Each time a branch is executed the table is updated. Several different schemes can be used for the BPB. The simplest scheme uses one bit to predict the outcome of a branch. If the branch is predicted *taken*, and resolves to *not-taken* then the bit is flipped, and vice-versa. However, this simple scheme causes branches to be mispredicted unnecessarily when a loop is executed several times in close proximity. Modifying the BPB to use a two bit prediction scheme solves the problem.

#### 2.2.2 Correlating Predictors

While the two bit scheme used in the BPB is an improvement over the one bit scheme, only the recent behavior of *one* branch is taken into consideration when trying to predict the behavior of a branch. If the behavior of other branches are taken into consideration when predicting branch outcomes, then more accurate predictions can be made. *Correlating predictors* (two-level predictors) use the behavior of multiple instances of previous branches to help make predictions.

Correlating predictors can be generalized to use the behavior of the last m branches to choose from among  $2^m$  predictors, each having n bits. This generalized form of correlating predictors is called an (m, n) predictor. A shift register can be used to record the behavior of the last m branches, where each bit in the shift register represents whether one of the previously executed branches was *taken* or *not-taken*.

#### 2.2.3 Tournament Predictors

Tournament or hybrid predictors simply combine two or more prediction methods together, taking into account that different prediction methods may work better for different types of branches. In work done by Scott McFarling [3], two types of predictors are combined and an array of two bit saturating counters is used to determine which branch prediction method to use. McFarling conducted experiments, in which the two prediction methods were *bimodal* and *gshare* prediction. In these experiments the tournament predictor consistently outperformed each technique performed in isolation [3].

#### 2.2.4 Markov Predictors

Recent work in the field of branch prediction [4, 5] applies techniques common in the field of data compression to the problem of branch prediction. It is shown in work done by Chen, et. al., that *correlating* or *two-level* predictors are a simplification of an optimal predictor used in data compression called *predication by partial matching* (PPM). Experiments indicate that PPM outperforms two-level predictors, however it may not be feasible to build optimal predictors given the current level of technology [4].

#### 2.2.5 Neural Methods for Branch Prediction

Neural methods of branch prediction try to find a simple neural method to use as an alternative to the commonly used two bit counters. One such neural method uses a *perceptron* predictor to replace the two bit counter [6]. A longer history length can be taken into account as part of the prediction, when using perceptron predictors, as the hardware resource for this method scales linearly, rather than exponentially, with the history length. Thus, perceptron predictors can consider much larger histories with the same resources as the two bit predictor. A perceptron is a learning device that takes a set of input values and combines them with a set of weights (learned though training) to produce an output value. In branch prediction, the weights represent the correlation between the current branch and the past behavior of other branches. The weight is incremented when a branch is *taken* and the weight is decremented when the branch is *not-taken*.

Experiments using perceptron predictors, carried out through simulation, showed improvements over McFarling style hybrid predictors [6], although the complexity of both the hardware and the computation is increased when using perceptron predictors. Thus, questions remain about the feasibility of realistically implementing this method without increasing the cycle time of the machine.

# 2.3 Branch Target Buffer

Even when hardware prediction successfully reduces the branch cost with an accurate branch prediction a delay may still occur while the branch target address is calculated. The BTB acts as a small cache of branch target addresses, which when given the address of a branch will return the actual target address.

Each entry of a BTB typically consists of a tag containing a portion of a branch instruction's address plus the branch's target address. The next several instructions following the branch target may also be located within the buffer. If the branch instruction's address is not in the BTB, then a prediction of *not-taken* occurs. If the prediction is incorrect, then the pipeline is stalled while the correct address is fetched. If a branch is predicted to be *taken* and resolves to *not-taken*, then the tag corresponding to that branch is deleted from the BTB. On the other hand, if a branch is predicted *not-taken* and resolves to *taken*, then the branch target address is inserted in the BTB. Branch target buffers and branch prediction buffers are often combined to gain the benefits of more accurate prediction methods.

## 2.4 Branch Registers

Another technique to reduce the cost of executing a branch uses traditional registers to hold the branch target address and the instructions corresponding to it [7]. In this research two machines were designed and emulated. The baseline version had 32 general-purpose registers and the other had 16 general-purpose registers and 16 registers that were used for branching. The calculation of the branch target address is separated from the instruction that performs the transfer of control. By exposing the computation of the branch target address to the compiler, this technique provides new opportunities for optimization. In many cases the calculation of the branch target address may be moved out of loops, thereby incurring the cost of the calculation once per loop.

## 2.5 Predication

Predicated execution is the conditional execution of an instruction based upon the value of a boolean source operand, called the *predicate*. Predicated instructions are fetched regardless of the value of their predicate. Instructions whose predicate value is *true* execute normally. Instructions whose predicate value is *false* are nullified.

There are multiple benefits when an architecture has support for predicated execution. First, reducing the number of a branches reduces the need to sustain multiple branches per cycle. Second, eliminating frequently mispredicted branches leads directly to the substantial elimination of branch mispredictions. Finally, predicated execution helps the compiler expose multiple paths of execution to the hardware. While the potential benefits for predicated execution are high, there are some costs involved. An instruction set must be designed that increases the number of source operands for all instructions in order to include the predicate operand.

Since all instructions in an architecture that supports full predication depend upon the predicate source operand, instructions must be added to the instruction set that efficiently modify the predicate registers. These instructions must be able to store, set, load, clear and define predicates.

#### 2.6 Loop Transformations

Many classic code improving transformations that are performed by compilers as part of the optimization process involve loop transformations. Many of these loop transformations reduce loop overhead, which may reduce the number of branches executed during the run of a program. This paper discusses two of the most common loop optimizations, both of which help reduce the number of branches executed.

#### 2.6.1 Loop Unrolling

Loop unrolling [8, 9] replicates the body of a loop n number of times, where n is the *loop unrolling* factor. The loop control code, must then be modified accordingly so that the loop behavior is preserved. Unrolling not only reduces the overhead of the loop, thus reducing the number of branches executed, but also provides new opportunities for other code improving transformations to be applied. However, loop unrolling can have a negative impact on the instruction cache since the unrolled loops are larger then the original loops.

#### 2.6.2 Loop Unswitching

Loop unswitching [8, 10] is applied to loops that contain a branch with loop invariant conditions. The loop is replicated inside each fork of the branch, which saves the overhead of executing the comparison and branch on each iteration of the loop. This code improving transformation can reduce loop overhead and possibly enable parallelization.

# 2.7 Avoiding Conditional Branches

Other techniques use code duplication to try to remove conditional branches. These techniques try to find paths where the result of a branch is known and then duplicate code to take advantage of that fact. These code improving transformations can be viewed as a form of *partial redundancy elimination* for conditional branches.

#### 2.7.1 Intraprocedural Conditional Branch Elimination

In the intraprocedural technique discussed in [11], the compiler must determine if branches can be avoided. To do this the compiler first calculates the set of registers and variables upon which the comparison associated with a branch depends. Next, the compiler attempts to determine if there exists a path from the point immediately after a conditional branch to the same path upon which the comparison is not affected. This is accomplished by calculating, for each block, an *in* and *out* state indicating the branches whose results are known at the beginning of the block and at the end of the block. A branch can become known at points within the control flow when a branch is executed, another branch subsumes the branch in question, or as an effect of some other instruction or side-effect in a block. Just as a branch can become known in a block, it can become unknown due to being affected by another instruction. A separate algorithm is used to duplicate paths where the state of the branch is known. In this case the branch can either be eliminated or converted to an unconditional jump.

#### 2.7.2 Interprocedural Conditional Branch Elimination

The technique discussed in this section is very similar to the technique discussed in Section 2.7.1, and while both techniques eliminate conditional branches, the technique presented in this section works interprocedurally [12]. The compiler determines whether an interprocedural path exists along which a branch outcome is known at compile time, and then tries to eliminate it through code restructuring. If the path in question is affected by a procedure call, then the code restructuring involves *entry splitting* and *exit splitting*. These splitting techniques create multiple entries to a procedure and multiple exits from a procedure, respectively. The interprocedural conditional branch elimination technique presented here is demand driven, to avoid excessive computation and analysis of the program. Also the algorithm never increases the number of operations along a path through an interprocedural flow graph.

# 2.8 Transforming Conditional Branches into Indirect Jumps

Traditionally indirect jumps from tables are only generated when a compiler translates multiway select statements, such as the C switch statement. However, indirect jumps from tables can be used to replace sequences of branches which compare the same register or variable to some constants [13]. Creating efficient indirect jumps in the front end of a compiler is difficult. It is hard to know how instructions can be efficiently used in a machine independent environment, this is more effectively done after the machine instructions have been generated. Also opportunities for code improving transformations may be missed when indirect jumps are generated in the front end of a compiler. The technique discussed in this section advocates waiting until after code generation to create indirect jump tables as part of a general purpose transformation.

Performing an indirect jump from a table has been traditionally considered an expensive operation. It involves performing range checks, calculating the address of the table, calculating an offset into the table itself, loading the target from the jump table, and finally performing the jump itself. To make these jumps more efficient, several optimizations, such as padding the table and byte addressing may be applied.

#### 2.9 Compiler Support for Predicated Execution

Predicated execution refers to the conditional execution of instructions based upon the value of a boolean source operand, called the *predicate*. The process of eliminating conditional branches from a program to use predicate support is called *if-conversion* [14, 15, 16]. However, using existing compiler support for architectures that support predicated execution has several problems. Typical uses of *if-conversion* combine all execution paths in a region into a single block. This forces instructions from the entire region to be examined *every* time a particular path is entered. The inclusion of infrequently executed paths and paths with a relatively large number of instructions can degrade the performance of the *if-converted* code. In addition, paths that have procedure calls or unresolvable memory accesses can also hinder optimizations phases and instruction selection.

#### 2.9.1 The Hyperblock

A structure called the hyperblock [17] is used to overcome these problems. A hyperblock is a sequence of basic blocks in which control may enter only from the top (like basic blocks themselves). However, control may exit from one or more locations. Hyperblocks are similar to superblocks [18], but superblocks are not predicated and thus contain instructions from only one flow of control, while hyperblocks are predicated and may contain instructions from multiple flows of control. To extend a traditional compiler to more efficiently generate code for machines supporting predicated execution, we must select the basic blocks to be included in the hyperblocks, take the blocks selected and actually transform them into a hyperblock, and add some extensions to the compiler itself to be able to work with this new structure.

Not all basic blocks, to which control flows, are necessarily included within a hyperblock. Including all the basic blocks would combine all paths of execution, which could lead to a degradation of performance due to limited machine resources. Basic blocks are examined, with the goal of including them in a hyperblock, according to three criteria. The execution frequency of the block is considered because we want to exclude non-frequently executed blocks. Next, the size of the basic block is taken into account. Basic blocks of smaller size are given higher priority for inclusion as large blocks use more machine resources and may reduce performance. Finally, the characteristics of the instructions within the basic block are examined. Basic blocks that contain hazardous instructions, such as divides and unresolvable memory access are given less priority.

# 2.10 Control CPR for EPIC Architectures

EPIC architectures use three main features to facilitate compile time predication. Explicit parallel issue, speculation, and predication. To totally exploit EPIC processors compilers must transform and schedule application programs to make parallelism more available at run-time. The amount of parallelism in application programs is limited by both data dependencies and control dependencies.

Critical path reduction (CPR) is a set of techniques for transforming programs to reduce both data and control dependencies, thus enhancing parallelism. Irredundant consecutive branch method (ICBM) [19] is form of control CPR [20]. ICBM can greatly reduce the number of branches executed, which can improve performance. With traditional control flow techniques, operations are confined to basic blocks which are guarded by branches. Predication is used to guard operations without confining them to basic blocks, using *if-conversion*. Earlier work in if-conversion [21, 17] primarily eliminated branches within single-entry, single-exit program regions. Dependent chains of branches were not treated and remained dependent during program scheduling. With ICBM the program is partitioned into single entry acyclic regions and a predicate is associated with each region. The computation of these predicates and their use to guard blocks eliminate dependencies between non-speculative operations, which includes branches. These predicates are called *fully resolved predicates* (FRPs). The goal of ICBM is to reduce the critical path length by transforming code without increasing the average number of executed instructions, this is accomplished in part by moving branches off-trace.

#### 2.11 TERA Computer System

The Tera architecture, a multistream MIMD system, was designed to be suitable for high speed implementations, to be applicable to a wide variety of problems, and for ease of compiler implementation. The first implementation of the architecture has 256 processors, 512 memory units, 256 input/output cache units, 256 input/output processors, 4096 interconnection network nodes and a clock cycle of 3 nanoseconds [22]. To help reduce branch costs, the Tera architecture has multiple versions of most operations, those that emit condition codes, and those that do not. When a branch occurs, it can examine a subset of the last 4 condition codes produced and branch accordingly. There are 8 target registers that are used as branch targets. The calculation of the branch target is separate from the decision to branch, allowing hardware to prefetch the instructions that calculate the branch target.

# CHAPTER 3

# CONDITION MERGING

# 3.1 Introduction

Conditional transfers of control occur frequently in programs, particularly in non-numerical applications. Conditional transfers of control are an impediment to improving performance since they consume a significant percentage of execution cycles, cause pipeline flushes when mispredicted, and can inhibit the application of other code-improving transformations. Techniques to reduce the number of executed branch instructions or remove branches from the control flow have the potential for significantly improving performance.

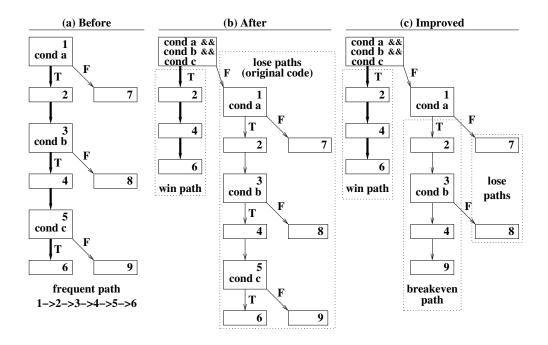

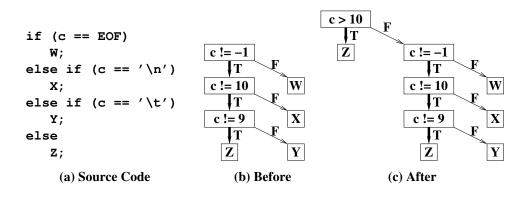

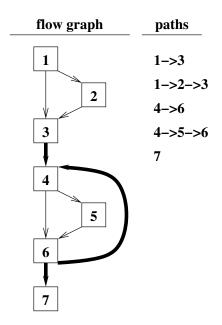

One approach to reducing the cost of conditional transfer of control is to attempt to merge a set of conditions together. Consider Figure 3.1(a), which shows conditions being tested in basic blocks 1, 3, and 5. The wider transitions between blocks shown in figures in this chapter represent the more frequently executed path, which occurs in Figure 3.1 when conditions a, b, and c are all satisfied. Figure 3.1(b) depicts the three conditions being merged together. If the merged condition is true, then the original conditions need not be tested. Note merging conditions results in the elimination of both comparison and branch instructions<sup>1</sup>. The elimination of the forks in the control flow between blocks 2, 4, and 6 may enable additional code-improving transformations to be performed. If the merged condition is not

<sup>&</sup>lt;sup>1</sup>Blocks 2 and 3 in Figure 3.1(a) could have been represented as a single block. Throughout the chapter we represent basic blocks containing a condition as having no other instructions besides a comparison and a conditional branch so the examples may be more easily illustrated.

Figure 3.1: Merging Three Conditions

satisfied, then the original conditions are tested. Figure 3.1(c) shows that branches can become redundant after merging conditions. In this case, condition c must be false if (a && b && c) is false and (a && b) is true. Thus, the branch in block 5 can be replaced by an unconditional transition to block 9. We call this the *breakeven* path since the same number of branches will be executed in this path as were executed in the original path. We only apply the condition merging transformation when we estimate that the total instructions executed will be decreased.

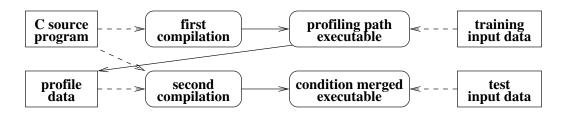

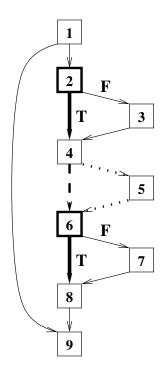

In this chapter we describe techniques to replace the execution of a set of two or more branches with a single branch. Figure 3.2 presents an overview of the compilation process for merging conditions. A first compilation pass produces an executable file that is instrumented to collect path profiling information. A second compilation pass uses the profile data to merge conditions in the frequently executed paths. The C front-end used in this research is *lcc* [23] and the back-end used is VPO [24] targeted to the SPARC architecture. For our test programs these techniques on average decrease the number of branches by 15.81% (0.82% to 59.62%),

Figure 3.2: Compilation Process for Merging Conditions

the number of instructions by 5.74% (0.14% to 40.34%), and the execution time by 3.43% (-4.15% to 25.59%). These improvements were automatically obtained by the compiler on a conventional scalar processor.

#### 3.2 Merging Conditions that Involve a Single Variable

In this section, we describe techniques to merge a set of conditions where each branch compares the same variable to invariant values (e.g., constants). In each case, the variable's value must not be unpredictably updated between the branches in the path.

#### 3.2.1 Eliminating Logically Redundant Branches

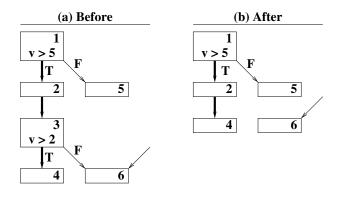

Sometimes the conditions associated with two or more branches are logically correlated. In other words, one branch result (taken or fall through) may imply the result of another. Consider Figure 3.3(a). If the condition for the branch in block 1 is satisfied, then v > 5. If v is not affected between the execution of the two branches, then v > 2 is guaranteed to be satisfied and the branch in block 3 can be deleted, as shown in Figure 3.3(b). Other techniques using static analysis and code duplication could also eliminate the branch in block 3 [11, 12].

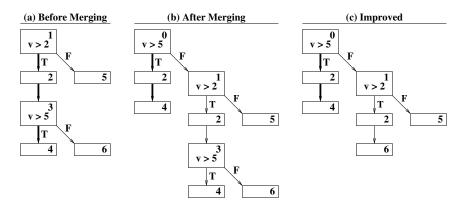

A path-based approach using profile data can be used to merge conditions that could not be merged using static analysis alone. Consider the flow graph in Figure 3.4(a). Satisfying the condition in block 1 will not guarantee the result of the branch in block 3. However, when the condition of the branch in block 3 is

Figure 3.3: Merging Logically Redundant Conditions

Figure 3.4: Merging Other Logically Redundant Conditions

satisfied, then the condition in block 1 is guaranteed to be also satisfied. If the path  $1 \rightarrow 2 \rightarrow 3 \rightarrow 4$  is the frequent path, then the second branch testing the condition v > 5 can be tested first, as shown in Figure 3.4(b). When the path  $0 \rightarrow 1 \rightarrow 2 \rightarrow 3$  is taken, the condition of the branch in block 3 is guaranteed to be false since the same condition has already been shown to be false in block 0.

Dynamo, a dynamic optimization system [25], could also merge conditions like the ones depicted in Figure 3.4(a). However, in many cases, our technique is able to further improve the code by restructuring the flow graph. For example, the branch in block 3 is eliminated, as shown in Figure 3.4(c), since the test is now redundant.

Performing the code-improving transformation results in one less branch executed when path  $0 \rightarrow 2 \rightarrow 4$  is taken, the same number of branches executed when the path  $0 \rightarrow 1 \rightarrow 2 \rightarrow 6$  is taken, and one additional branch executed when the path  $0 \rightarrow 1 \rightarrow 5$  is taken. The actual improvement would depend on the frequency that each path is taken. However, a benefit can be obtained when the *win* path  $0 \rightarrow 2 \rightarrow 4$ , which reduces the number of branches, is taken more frequently than the *lose* path  $0 \rightarrow 1 \rightarrow 5$ , which increases the number of branches. Thus, improvements may be obtained even when the *break-even* path  $0 \rightarrow 1 \rightarrow 2 \rightarrow 6$  is the most frequently executed path.

#### 3.2.2 Merging Not Equal Tests Using Range Checks

A single variable is often checked to determine if it is equal to one of a set of constants. For example, Figure 3.5(a) shows the variable c being compared to three different character constants. Figure 3.5(b) depicts the flow graph representing these tests. It is often the case that a variable involved in such tests is not equal to any of the constants [26, 27]. Profile data is collected to determine not only the paths that are frequent, but also the reason that a particular transition was taken. For instance, when a variable is involved in a test to see if it is equal or not equal to a constant and the not equal transition is taken, then profile data is collected to determine if the variable was greater than or less than the constant. The compiler uses this profile information during the second compilation pass to determine the most likely range of values, which a particular variable may have, when it is not equal to any of the specified constants. If this range is greater than or less than all of the specified constants, then the set of branches can be replaced with a single branch. Figure 3.5(c) shows that the three branches testing the variable c can be bypassed by checking if c is larger than the largest specified constant. Note that when the merged condition is not satisfied, the original set of branches must be tested since the variable could still be equal to any of the specified constants. By performing condition merging on frequent paths, we can merge conditions separated by other intervening branches, which is not possible using a non-path based approach [26, 27].

Figure 3.5: Merging Not Equal Tests Using Range Checks

Figure 3.6: Merging Bit Tests

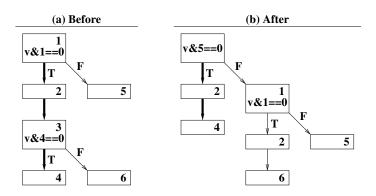

#### 3.2.3 Merging Bit Tests

Different bits in a single variable are sometimes tested to see if they are clear or set. Figure 3.6(a) shows two different bits in the same variable being tested to see if they are clear. If the profile data indicates that one combination of bits is very likely, then that combination of bits can be tested in a single comparison by changing the constant being compared, as depicted in Figure 3.6(b). When the merged condition is not satisfied, both bits cannot be clear. If we reach block 1 from the block containing the merged condition, then we know that satisfying both conditions cannot occur since the merged condition failed. If we reach block 2 from block 1, then we know that the first condition is true. Thus, the second condition must be false and the branch in block 3 can be eliminated.

| General Bit Test                   |                             |  |  |

|------------------------------------|-----------------------------|--|--|

| r[t]=r[v]&mask                     | # bitwise AND               |  |  |

| <pre>IC=r[t]?desired_value;</pre>  | # comparison                |  |  |

| <pre>PC=IC!=0,off_trace;</pre>     | # branch                    |  |  |

| Testing If Multiple Bits Are Clear |                             |  |  |

| <pre>IC=(r[v]&amp;mask})?0;</pre>  | # bitwise AND comparison    |  |  |

| <pre>PC=IC!=0,off_trace;</pre>     | # branch                    |  |  |

| Testing If Multiple Bits Are Set   |                             |  |  |

| r[t]=mask;                         | # loop-invariant assignment |  |  |

| IC=(r[t]&~r[v])?0;                 | # bitwise ANDNOT comparison |  |  |

| <pre>PC=IC!=0, off_trace;</pre>    | # branch                    |  |  |

Table 3.1: SPARC Code Generation Strategies for Merged Bit Tests

Table 3.1 shows different sequences of SPARC instructions represented as RTLs (register transfer lists) that can be used to test a set of bits. RTLs are machine and language-independent representations of machine specific instructions, used by many compilers as an intermediate language, including GCC and VPO (Very Portable Optimizer) [24], which is the compiler used to conduct this research. The first portion of the table shows a general sequence of three instructions that can be used to test if a set of bits has a specific combination of bits set. r[v] is a register containing the value of the variable. r[t] is a temporary. Mask is a constant that indicates the set of bits to be tested. *Desired\_value* is the value of the bits that will result in the frequent path being taken. The branch is taken when the set of bits in the variable does not have the desired value. The second portion of the table shows that the sequence can be reduced to two instructions when the desired value is to have all of the bits clear. All integer ALU operations requiring a single cycle on the SPARC also have the option of performing a comparison to zero to set the integer condition codes. The third portion depicts the sequence of instructions we used when the desired value has all of the specified bits in the mask set. The SPARC has ANDNOT and ORNOT instructions that perform a bitwise NOT of the second operand before performing the logical operation. If the variable has all of the desired bits set, then the bitwise

NOT will cause all of the desired bits to be clear. Hence, the ANDNOT operation allows a comparison with zero. The first instruction assigning the mask value is loop invariant and the cost can be reduced by performing loop-invariant code motion if the branch is inside a loop and a register is available to hold the value of the mask.

Integer flags are commonly used in many applications. In effect, such variables are used as booleans, which requires only a single bit to be represented. Our system automatically reduces integer global and local scalar variables to bits within a global or local flags variable when such a scalar is only assigned constant values and is only dereferenced for i = 0 and  $i \neq 0$  tests.

We accomplish the reduction of integer scalars to bits in a flag variable by examining and updating the *l*cc intermediate code files comprising the program. The assignment of nonzero constants to such a variable is replaced by a bitwise OR operation that sets a specific bit of a flag variable. The assignment of zero to such a variable is replaced by a bitwise AND operation that clears a specific bit of a flag variable. The i = 0 and  $i \neq 0$  tests of the scalar variables are replaced by bitwise AND tests of the appropriate bit of the flag variable.

There are several advantages to reducing integer scalar variables to bits within a flag variable besides being able to merge conditions performing bit tests. Consider the SPARC instructions shown in Figure 3.7(a). Multiple assignments that set specific bits are merged by assigning the bitwise OR of the constants, as shown in Figure 3.7(b). Likewise, Figure 3.7(c) depicts that multiple assignments that clear specific bits are also merged. Redundant loads of the same flag variable are eliminated, as illustrated in Figure 3.7(d). Finally, Figure 3.7(e) shows that redundant stores are also eliminated. Note that the elimination of redundant loads and stores would not be possible if separate integer scalar variables were used. Performance conscious programmers often employ such techniques by hand, which is a tedious and error prone task. We are not aware of any prior work that automates this approach.

| <pre>r[5] = M[flag];<br/>r[5] = r[5]   4;<br/>r[5] = r[5]   16;<br/>M[flag] = r[5];<br/>r[5] = M[flag];<br/>r[5] = r[5] &amp; ~2;<br/>r[5] = r[5] &amp; ~8;<br/>M[flag] = r[5];</pre> (a) Original Instructions |                                                                                                                     | r [5<br>M[f<br>r [5<br>r [5<br>r [5<br>M[f | <pre>b) = M[flag];<br/>b) = r[5]   20;<br/>clag] = r[5];<br/>b) = M[flag];<br/>b) = r[5] &amp; ~2;<br/>b] = r[5] &amp; ~8;<br/>clag] = r[5];<br/>After Merging<br/>ment Setting Bits</pre> |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|--------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <pre>r[5] = M[flag];<br/>r[5] = r[5]   20;<br/>M[flag] = r[5];<br/>r[5] = M[flag];<br/>r[5] = r[5] &amp; ~10;<br/>M[flag] = r[5];</pre>                                                                         | <pre>r[5] = M[flag];<br/>r[5] = r[5]   20;<br/>M[flag] = r[5];<br/>r[5] = r[5] &amp; ~10;<br/>M[flag] = r[5];</pre> |                                            | r[5] = M[flag];<br>r[5] = r[5]   20;<br>r[5] = r[5] & ~10;<br>M[flag] = r[5];                                                                                                              |

| (c) After Merging<br>Assignment Clearing Bits                                                                                                                                                                   | (d) After Removing<br>Redundant Loads                                                                               |                                            | (e) After Eliminating<br>Redundant Stores                                                                                                                                                  |

# Figure 3.7: Other Benefits from Reducing Scalars to Single Bits3.3 Merging Conditions that Involve Multiple Variables

The previous section described techniques for merging sets of conditions that compare a single variable to invariant values. In this section we describe techniques for merging sets of conditions that involve multiple variables.

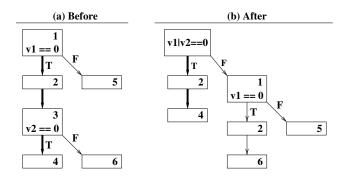

#### 3.3.1 Merging into a Single Equivalent Condition

We use logical operations to efficiently merge conditions that compare multiple variables to 0 or -1 into a single equivalent condition. Consider the flow graph shown in Figure 3.8(a). The frequent path checks if the two variables are equal to zero. Figure 3.8(b) depicts the two conditions being merged together using a bitwise OR operation. Only when both variables are equal to zero will the result of the OR operation be zero. Again, if the merged condition is not satisfied, then testing the condition v2 = 0 is unnecessary since it cannot be true.

Unlike the methods presented in the previous section, the number of instructions required to merge conditions involving multiple variables is proportional to the number of different variables being compared. Figure 3.9 shows the general code generation strategy we used for merging such a set of conditions.  $r[1] \dots r[n]$  represent

Figure 3.8: Merging Conditions That Test If Different Variables Are Equal to Zero

```

r[t] = r[1] | r[2];

r[t] = r[t] | r[3];

...

IC = (r[t] | r[n]) ? 0;

PC = IC != 0, <off-trace target>;

```

# Figure 3.9: Code Generated for the Merged Condition That Checks If n Variables Are Equal to Zero

the registers containing the values of n different variables. r[t] represents a register containing the temporary results. When merging conditions comparing n multiple variables, n-1 logical operations and a single branch replace 2n instructions (n pairs of comparisons and branches).

Table 3.2 shows how sets of conditions comparing multiple variables  $(v_1 \dots v_n)$  to 0 and -1 can be merged into a single condition. Column one gives the rule number, column two depicts the original condition, column three depicts the merged condition, and column four represents the percentage of time the rule was selected during testing compared to the other rules shown in Table 3.2 and Table 3.3. Rule 1 has been illustrated in Figures 3.8 and 3.9. Rule 2 uses the SPARC ORNOT instruction to perform a bitwise NOT on an operand before performing a bitwise OR operation. A word containing the value -1 has all of its bits set in a two's complement representation. Thus, if the operand is a -1, then the result of the bitwise NOT would be 0 and at that point the first rule can be used. The merged

Table 3.2: Rules for Merging Conditions Comparing Multiple Variablesinto a Single Equivalent Condition

| Rule | Original Conditions                      | Merged Condition                  | % Applied |

|------|------------------------------------------|-----------------------------------|-----------|

| 1    | $v_1 = 0 \&\& \cdots \&\& v_n = 0$       | $(v_1   \cdots   v_n) = 0$        | 42.7%     |

| 2    | $v_1 = 0 \&\& \cdots \&\& v_n = -1$      | $(v_1   \cdots   \sim v_n) = 0$   | 0.0%      |

| 3    | $v_1 < 0 \&\& \cdots \&\& v_n < 0$       | $(v_1 \& \cdots \& v_n) < 0$      | 0.0%      |

| 4    | $v_1 \geq 0 \&\& \cdots \&\& v_n \geq 0$ | $(v_1   \cdots   v_n) \ge 0$      | 4.5%      |

| 5    | $v_1 < 0 \&\& \cdots \&\& v_n \ge 0$     | $(v_1 \& \cdots \& \sim v_n) < 0$ | 0.9%      |

| 6    | $v_1 \ge 0 \&\& \cdots \&\& v_n < 0$     | $(v_1   \cdots   \sim v_n) \ge 0$ | 0.0%      |

condition in rule 3 performs a bitwise AND operation on the variables. A negative value in two's complement representation has its most significant bit set. Only if the most significant bit is set in all of the variables will the most significant bit be set in the result of the bitwise AND operation. If the most significant bit is set in the result, then the result value will be negative. The merged condition in rule 4 performs a bitwise OR operation on the variables. A nonnegative value in a two's complement representation has its most significant bit clear. Only if the most significant bit is clear in all the variables will the most significant bit be clear in the result of the bitwise OR operation. The last two rules perform a bitwise NOT on an operand, which flips the most significant bit along with the other bits in the value. This allows '<' and '>=' tests to be merged together.

Notice that '> 0' and ' $\leq = 0$ ' tests are not listed in the table. A '> 0' test would have to determine that both the most significant bit is clear and that one or more of the other bits are set. These types of tests cannot be efficiently performed using a single logical operation on a conventional scalar processor.

Additional opportunities for condition merging become available when sets of conditions, which cross loop boundaries, are considered. It would appear that in Figure 3.10(a) there is no opportunity for merging conditions. However, Figure 3.10(b) depicts that after loop unrolling there are multiple branches that use the same relational operator. Our system merges sets of conditions across loop iterations.

```

for (i = 0; i < 10000; i++)

if (a[i] < 0)

x;

(a) Original Code</pre>

for (i = 0; i < 10000; i += 2) {

if (a[i] < 0)

x;

if (a[i] < 0)

x;

if (a[i+1] < 0)

x;

}

}

```

#### (b) After Loop Unrolling

Figure 3.10: Increasing Merging Opportunities by Unrolling Loops In order to simplify the analysis, we only merge conditions that span two consecutive iterations of a loop.

#### 3.3.2 Merging into a Sufficient Condition

Our system also uses logical operations to efficiently merge conditions, which compare multiple variables, into a single sufficient condition. In other words, the success of the merged condition will imply the success of the original conditions. However, the failure of the merged condition does not imply the original conditions were false. Table 3.3 shows rules for merging conditions containing multiple variables into a single sufficient condition. The columns in this table contain similar information to the columns in Table 3.2.

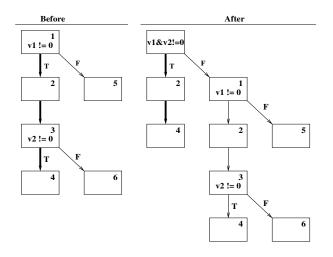

There were no ' $\neq$  0' tests listed in Table 3.2. Yet tests to determine if a variable is *not-equal* to zero occur frequently in programs. We can determine if two or more variables are guaranteed to be not equal to zero by performing a bitwise AND operation on the variables and checking if the result does not equal to zero, as shown in rule 7 of Table 3.3. Note that failure of the merged condition does not imply that the variables are all not equal to zero.

One may ask how often such conditions can be successfully merged in practice. Consider the code segment:

if (p1 != NULL && p2 != NULL)

Table 3.3: Rules for Merging Conditions Comparing Multiple Variables

into a Single Sufficient Condition

| Rule | Original Conditions                          | Merged Condition                                         | % Applied |

|------|----------------------------------------------|----------------------------------------------------------|-----------|

| 7    | $v_1 \neq 0 \&\& \cdots \&\& v_n \neq 0$     | $(v_1 \& \cdots \& v_n) \neq 0$                          | 18.2%     |

| 8    | $v_1 \neq c_1 \&\& \cdots \&\& v_n \neq c_n$ | $(v_1 \& \cdots \& v_n) \& ~(c_1   \cdots   c_n) \neq 0$ | 15.5%     |

| 9    | $v_1 \neq c_1 \&\& \cdots \&\& v_n \neq c_n$ | $  (v_1   \dots   v_n) \& (c_1   \dots   c_n) \neq 0$    | 16.4%     |

| 10   | $v_1 < c_1 \&\& \cdots \&\& v_n < c_n$       | $(v_1   \cdots   v_n) u < \min(c_1, \cdots, c_n)$        | 1.8%      |

Figure 3.11: Merging Conditions That Check If Different Variables Are Not Equal to Zero

where two pointer variables, p1 and p2, are tested to see if they are both non-NULL. In most applications, a pointer variable is only NULL in an exceptional case (e.g., end of a linked list). It is extremely likely that two non-NULL pointer values will have one or more corresponding bits both set due to address locality. Figure 3.11 shows how two or more conditions checking if multiple variables are not equal to zero can be merged. If the merged condition is not satisfied, then the entire original set of branches still needs to be tested.

We are also able to merge conditions that check if multiple variables are all not equal to a specified list of constants. One method we used is to check if any bits set in all of the variables are always clear in all of the constants. Rule 8 of Table 3.3 depicts how this is accomplished, where  $c_1 \dots c_n$  are constants. A bitwise AND

$$(v_1\&\cdots\&v_n)\&\sim(c_1|\cdots|c_n)\neq 0$$

$$(v_1\&\cdots\&v_n)\&\sim(0|\cdots|0)\neq 0$$

$$(v_1\&\cdots\&v_n)\&\sim(0)\neq 0$$

$$(v_1\&\cdots\&v_n)\&0xFFFFFFF\neq 0$$

$$(v_1\&\cdots\&v_n)\neq 0$$

#### Figure 3.12: Rule 7 is Implied by Rule 8

operation is performed on all of the variables to determine which bits are set in all of these variables. The complement of the bitwise OR of the constants is taken, which results in the bits being set that are clear in all of the constants. Note that determining which bits in the constants are always clear is determined at compile time. If any bits set in all of the variables are clear in all of the constants, then it is known that all of the variables will not be equal to all of the constants. Rule 8 in Table 3.3 can also be used when the constants are all zero. Figure 3.12 shows how the merged condition in rule 8 simplifies to the merged condition in rule 7 when  $c_1 \dots c_n$  are all zero.

Another method to determine if multiple variables are not equal to a list of constants is to check if one or more bits, which are clear in all of the variables, are set in all of the constants. Merging conditions using this method is shown in rule 9 of Table 3.3. The decision to use rule 8 or 9 is determined by checking the success of these rules during the profile run. Given an equal likelihood that either rule could be successfully applied, rule 8 is preferable since rule 9 requires an extra instruction to perform the bitwise NOT operation, which is accomplished at compile time for rule 8.

We found that rules 8 or 9 can be used when a single variable was checked to see if it was not equal to a set of constants. For instance, Figure 3.13 illustrates how rule 8 is simplified to only require a single bitwise AND operation to set the condition codes when only a single variable was involved. Thus, both the range checking method illustrated in Figure 3.5 and the bit testing methods using rules 8 or 9 are checked to estimate which would be most profitable.

$$(v_1\&\cdots\&v_1)\&\sim(c_1|\cdots|c_n)\neq 0$$

$$v_1\&\sim(c_1|\cdots|c_n)\neq 0$$

#### Figure 3.13: Using Rule 8 Efficiently with a Single Variable

We are also able to merge conditions checking if multiple variables are less than (or less than or equal to) constants. Rule 10 in Table 3.3 depicts how this is accomplished, where  $c_1 \ldots c_n$  must be positive constants and the u < in the merged condition represents an unsigned less than comparison. If the result of the bitwise OR on the variables is less than the minimum constant, then the original conditions have to be satisfied. The unsigned less than operator is necessary since one of the variables could be negative and the result of the bitwise OR operation would be treated as a negative value if a signed less than operation is used.

Our system merges conditions comparing multiple variables to values that are not constants. Consider the original loop and unrolled loop shown in Figure 3.14(a) and Figure 3.14(b), respectively. It would appear there is no opportunity for merging conditions. However, x is loop invariant. Thus, bits that are set in both a[i] and a[i + 1] can be ANDed with  $\sim x$  to determine if the array elements are not equal to x, as shown in Figure 3.14(c). The expression  $\sim x$  is loop invariant and the compiler will move it out of the loop when loop-invariant code motion is performed. Likewise, the loads of the two array elements in the *else* case will be eliminated after applying common subexpression elimination. Note we are also able to merge conditions checking if multiple variables are not equal to multiple loop invariant values. The profitability of using rules 8 and 9, where  $c_1 \dots c_n$  could be loop invariant values, is estimated during the profile run.

Figure 3.15 shows another example where conditions comparing multiple unsigned variables to non-constants can be merged. When finding the largest value in an array, it is very likely that most of the elements examined will not be greater than the maximum value found so far. When merging the less than or equal tests, the value (max in this case) being compared to the variables needs to be the same value

```

for (i=0; i < 10000; i++)</pre>

if (a[i] == x)

for (i=0; i < 10000; i +=2) {</pre>

num++;

if ((a[i] & a[i+1]) & ~x)

(a) Original Code

continue;

else{

if (a[i] == x)

for (i=0; i < 10000; i += 2) {</pre>

num++;

if (a[i] == x)

if (a[i+1] == x)

num++;

num++;

if (a[i+1] == x);

}

num++;

}

}

(c) After Condition Merging

```

(b) After Loop Unrolling

## Figure 3.14: Merging Conditions That Check If Multiple Variables Are Not Equal to Loop-Invariant Values

(otherwise one would not know which would be the minimum) and has to be invariant in the path between the conditions.

## 3.4 Estimating the Benefit of Merging a Set of Conditions

In order to apply a condition merging transformation, the compiler needs to know which paths are frequently executed in the program. We extended the *EASE* environment [7] in the *VPO* compiler [24] to collect path profile information. We define a path as a sequence of blocks within a function that are either terminated by edges that cross loop boundaries or when a return block is reached. Consider the example flow graph that is shown in Figure 3.16. The edges that cross loop boundaries are  $3 \rightarrow 4$  (entering the loop),  $6 \rightarrow 4$  (backedge), and  $6 \rightarrow 7$  (exiting the loop). Statically enumerating all of the paths in a function according to this definition can sometimes result in an excessive number of paths. Thus, we decided to detect paths dynamically during the execution of the profile run. During the first compilation pass we modify the generated assembly to insert a call to an instrumentation routine at the beginning of each basic block. When this routine

```

max = 0;

for (1 = 0; i < 10000; i++)</pre>

if (a[i] > max)

max = 0;

max = a[i];

for (i = 0; i < 10000; i + = 2) {

(a) Original Code

if ((a[i] | a[i+1]) <= max)</pre>